利用I3C实现更快、更简单、更灵活的集成电路间通信

2025年01月03日 15:31 发布者:eechina

来源:Digikey作者:Art Pini

用于集成电路 (IC) 间通信的板载串行接口由内部集成电路 (I²C) 和串行外设接口 (SPI) 主导,两者自 20 世纪 80 年代起就已问世。这些接口广泛用于将低速传感器和 IC 连接到微控制器单元 (MCU),以实现板内短距离通信。然而,随着数字系统的速度越来越快,这些接口已成为限制因素,I²C 的典型数据速率仅为 1 Mbit/s,而 SPI 也不过 10 Mbit/s。其他限制因素,包括专用中断或芯片使能线路,需要额外的信号连接,这就增加了线数以及总线连接的复杂性。

改进型内部集成电路 (I3C) 总线旨在对 IC 间通信进行升级。该总线具有更高的数据速率、更大的灵活性,以及真正的双线接口,支持带内中断 (IBI) 而非外部中断。

本文讨论了 I3C 接口的特征,以及为什么说它是 I²C 和 SPI 串行接口的理想升级品。我们将使用典型的 MCU、IC 开关和传感器设备来展示其应用。

嵌入式通信总线

多年来,I²C 和 SPI 等嵌入式串行互连器件一直被用于板内通信。这些器件主要用作传感器和用户界面设备及其控制处理器之间的通信总线。典型系统中的传感器数量不断增加,在手机中已达到 10 到 20 个,在汽车中则更多。与此同时,随着对更高速度、更低功耗和更少导线的需求不断上升,对设计人员而言,通信要求也变得更具挑战性。设计人员必须满足这些要求,同时通过中断和使能线保持处理器控制(图 1)。

图 1:嵌入式通信应支持更高速度、更低功耗和最少线数。(图片来源:NXP Semiconductors)

现行技术使用两线制 I²C 或四线制 SPI 接口实现传感器和用户控制设备接口。中断、使能和其他控制线路与时钟和数据线路分开,因此每个接口有更多线路。

设计人员需要一种更具前瞻性的接口方法,这种方法可以消除互连器件中的这些额外导线,仅使用时钟和数据线路在带内处理这些操作。此外,总线应具有更高的运行速度,以及更低的功率损耗。

I3C 接口

为了满足这些要求,移动行业处理器接口 (MIPI) 联盟开发了 I3C。该接口面向 MIPI 会员提供 MIPI I3C,面向非会员提供功能简化版 MIPI I3C Basic。与传统的 I²C 和 SPI 接口一样,这种改进型也是串行接口,采用两线制,尽可能减少了引脚数以及元器件之间的信号路径数量。其数据速率高达 12.5 Mbits/s,采用单倍数据速率 (SDR) 模式,时钟频率为 12.5 MHz。该接口运行功率水平较低,采用简单而灵活的设计架构。

值得注意的是,I3C 标准保留了与 I²C 系统有限的向后兼容性,可让现有 I²C 设备连接到 I3C 总线,同时仍允许总线在符合 I3C 标准的设备之间进行通信时切换到更高的数据速率。系统配置的比较见图 2。

图 2:通过对 I3C、I²C 和 SPI 接口的基本配置进行比较,可以看出 I3C 的速度更快,布线更简单。(图片来源:NXP Semiconductors)

四线制 SPI 接口运行速度更快,并支持全双工通信。I²C 通过由时钟 (SCL) 和数据 (SDA) 线路组成的双线制总线进行半双工通信。两者都需要额外的线路来支持中断和其他控制功能(如片选)。I3C 将接口中使用的线数减少至两条,消除了 I²C 和 SPI 中单独使用的中断、使能和片选线路。对于需要 10 到 20 个传感器与处理器相连且每个传感器都有数条辅助线的系统来说,减少线数是一大优势。中断和其他控制线路被 IBI 取代。在这种方法中,目标传感器或设备会将其地址输入 I3C 总线地址标头,以通知处理器发生中断。

I²C 和 I3C 的时钟速率相差甚大。I²C 的时钟速率一般为 100 kHz、400 kHz 或 1 MHz,而 I3C 的时钟速率可达 12.5 MHz。以前,SPI 用于时钟速率高于 1 MHz 的应用。设计时需要在时钟速率与线数之间进行选择。I3C 采用真正的双线制拓扑结构,具有更高的时钟和数据速率,从而改变了这一现状。

推挽输出的开关速度比开漏或集电极驱动器更快,是 I3C 提高时钟速率的重要因素。为了保持与 I²C 设备的兼容性,I3C 可根据总线状态在开漏和推挽驱动器之间切换。开漏或集电极设计在初始寻址或仲裁期间使用,此时线路上可同时存在 I²C 和 I3C 设备。在进行单向通信时,I3C 采用推挽方式,不会出现 I²C 设备同时通信的情况。

除标准 SDR 外,I3C 还支持多种可选的高数据速率 (HDR) 模式。这些 HDR 模式以相同的时钟速率运行,但传输的数据密度更高。第一种 HDR 模式是 HDR 双倍数据速率 (HDR-DDR),数据在时钟信号的两个边沿进行传输,速率是原来的近两倍。对于 12.5 MHz 时钟,DDR 模式可实现 20 Mbits/s 的有效数据速率。

HDR 三元符号有两个版本:HDR 纯总线三元符号 (HDR-TSP) 仅适用于 I3C 设备,而 HDR 传统三元符号 (HDR-TSL) 则适用于包括 I²C 和 I3C 器件在内的总线。三元符号模式通过在 SCL 和 SDA 线路上编码三位(三元)符号来实现每个时钟三个数据位。

HDR 批量传输 (HDR-BT) 模式支持通过四路、双路或单路 SDA 数据线路进行通信,从而提供最高数据速率。因此,在相同的时钟速率下,这是原始单倍数据速率性能的 8 倍、4 倍或 2 倍。

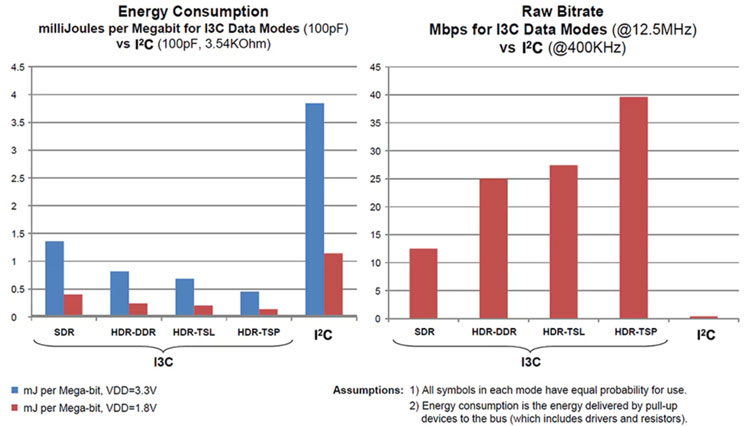

数据传输速度的提高使设备的启动时间更短,从而降低了总线功率占空比。这与 I²C 相比降低了功耗(图 3)。从带有外部上拉电阻器的开集驱动器转变为推挽驱动器进一步降低了功耗,因为上拉电阻器需要很大的功率才能运行。

图 3:与 I²C 相比,I3C 在数据速率和功耗方面均有改进。(图片来源:NXP Semiconductors)

寻址

I²C 对每个总线设备使用 7 位或 10 位长度的静态地址。这在 I3C 中已更改为 7 位动态寻址,即总线主设备在动态地址分配 (DAA) 时设置设备地址,并将其存储在设备寄存器中。在 I3C 中仍可像在 I²C 外设中一样使用静态寻址。

由于采用动态寻址,设备地址可在以后更改。这支持热连接,允许在总线运行时添加新设备。连接到 I3C 总线的新设备通过发送热连接请求向 I3C 主设备发出其存在的信号。主控制器确认请求并分配一个地址,以将设备添加到总线上。

IBI

I3C 是真正的双线制总线,使用 IBI 而不是 I²C 那样的专用中断线路。IBI 是指目标设备通过拉低 SDA 线路向主设备发出可用性信号的情况。然后,主设备会启动 SCL 线路上的时钟,目标设备将其地址传输到 I3C 总线上,以通知控制器发生中断。

常用命令代码

常用命令代码 (CCC) 是标准化命令,控制器可将其作为一般广播同时发送给所有 I3C 设备或特定目标设备。这些命令用于与总线管理有关的项目。CCC 协议的格式以 I3C 广播地址开始,总线上的所有 I3C 设备都能识别该地址。总线上的任何 I²C 设备都不会确认该请求,因为这是一个保留的 I²C 地址。

每条命令都包括一个 8 位描述符 ID 字段,后面还可能有一个命令有效载荷。向特定设备发送的命令会在有效载荷的第一个字节中传递设备地址。有四十多个 CCC 命令,包括:

· 输入动态地址分配 (ENTDAA)

· 设置新动态地址分配 (SETNEWDA)

· 启用事件 (ENEC)/禁用事件 (DISEC)

· 复位动态地址分配 (RSTDAA)

· 输入高数据速率模式 (ENTHDRx)

· 获取设备特征寄存器 (GETDCR)

供应商可以使用一系列专用的 CCC ID 来执行自己的命令。

错误检测和恢复

与 I²C 不同,I3C 包含错误检测和恢复功能。对于目标设备,有六种强制性错误和恢复方法,还有一种可选方法。此外,还有专门针对主设备端错误的其他错误和恢复方法。

支持 I3C 的元器件

如图 2(左)所示,基本的 I3C 网络至少包括一个主控制器和一个或多个 I3C 目标设备或从设备。主设备可以是 MCU,例如 NXP Semiconductors 的 LPC5534JHI48-00MP(图 4)。该器件是一款 32 位 Arm® Cortex®-M33 MCU,具有 128 KB SRAM 和 256 KB 闪存。其 Flexcomm 接口支持八个不同的串行接口,包括 I3C。

图 4:LPC5534JHI48/00MP MCU 包括一个 I3C 接口和其他七个串行接口。(图片来源:NXP Semiconductor)

I3C 总线允许添加作为从设备引入总线的辅助主设备。I3C 可以有多个主设备,但只能有一个是控制器。一旦注册,辅助主设备即可请求获取当前主设备状态,如果当前主设备同意,其控制权将移交给提出请求的辅助主设备。

NXP 的 P3T2030CUKAZ 就是一种典型的 I3C 传感器。该温度传感器可将 -40°C 至 +125°C 的温度转换为 12 位数值,精度为 ±2°C。该器件包括一个 I²C 和一个 I3C SDR 模式串行接口。

TDK InvenSense 的 ICM-42605 三轴微机电系统 (MEMS) 陀螺仪和加速计是更为复杂的传感器。作为速率陀螺仪,该器件可测量 ±15.2 至 ±2000 °/s 的旋转速率。而作为加速计,其量程为 ±2 至 ±15 g。该器件可检测运动、倾斜、轻击或步数(计步器)。作为 I3C 传感器,其在 SDR 模式下的工作频率为 12.5 MHz,在 DDR 模式下为 25 MHz。

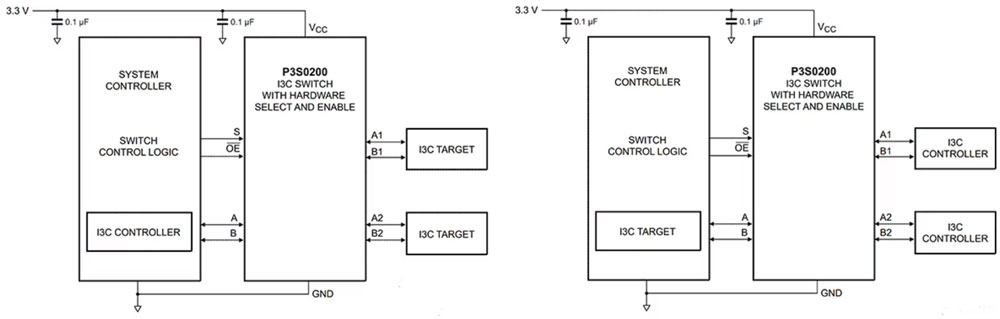

诸如 NXP P3S0200GMX I3C 开关之类的 IC 可在 I3C 控制器和多组目标设备之间,或在由外部 MCU 确定的单个目标设备和多个 I3C 控制器之间路由 I3C 总线信号,从而重新配置 I3C 总线(图 5)。

图 5:P3S0200GMX I3C 开关可用于在 I3C 控制器和多组目标设备之间,或在单个目标设备和多个 I3C 控制器之间路由 I3C 总线信号,从而重新配置 I3C 总线。(图片来源:NXP Semiconductors)

如果两个目标具有相同的地址,且不能位于同一总线上,则可能需要在两个目标之间进行切换。另外,两个进程可能须共享一个目标,这需要在两个 I3C 控制器之间进行切换。

结语

I3C 是一种串行接口,通过提高数据速率、减少线数和增加总线控制的灵活性来扩展 I²C 总线。这种增强版总线可扩展传统 I²C 和 SPI 接口的实用性。