�����·��ƾ��ϣ�����ʦ�ر�����!

2024��11��13�� 15:04 �����ߣ�yxcyangxing

������Ϊʱ�ӵ�·�бز����ٵ��źŴ����ߣ���Ƭ��Ҫ��������������Ҫ������ڡ���ˣ��ڵ��ӵ�·�����Ҳ�ٲ��˾���IJ��롣һ���õľ����·��ƣ����ܹ�Ϊ�����ṩ��õĿռ������ʣ�ͬʱ�������Ĺ��������á� ��ԭ��������һ��û�������źŵĴ�ѡƵ������������Ŵ������������ĽǶ���˵�����Ҳ�������ͨ���Լ���ʽ��ֱ������ת��Ϊ�ض�Ƶ�ʺͷ��ȵ����ҽ��������ĵ�·�������κ�һ�����з����ķŴ��·�������Ի�����ͼ��ʾ�ṹ��

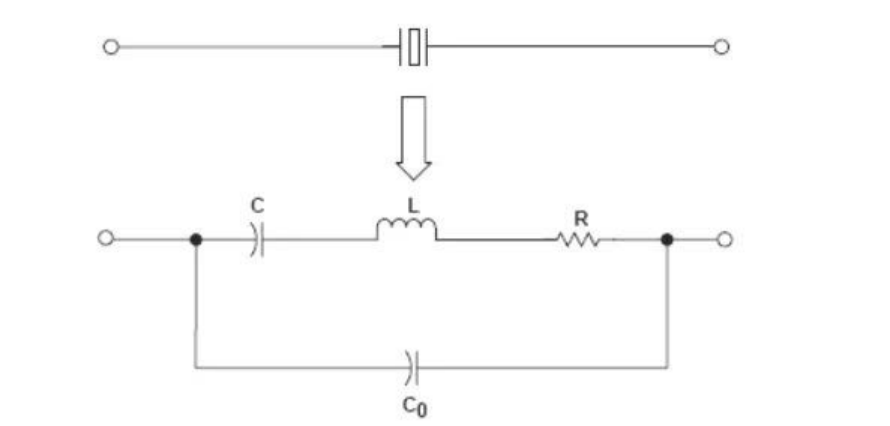

��ԭ��������һ��û�������źŵĴ�ѡƵ������������Ŵ������������ĽǶ���˵�����Ҳ�������ͨ���Լ���ʽ��ֱ������ת��Ϊ�ض�Ƶ�ʺͷ��ȵ����ҽ��������ĵ�·�������κ�һ�����з����ķŴ��·�������Ի�����ͼ��ʾ�ṹ�� ��ͼ1 ����

��ͼ1 ��������������Of�O���Oa�O��1������λ���������+��=2��nʱ��������������·�����������������㡣��ͼ������һ��������

����ԭ�����ھ������˼���һ���Ľ���糡����Ƭ�ͻ������е�α䣬ʯӢ��������������ʯӢ�����ѹ��ЧӦ�Ƶ�һ��г������������ʯӢ����������缫�ϼ�һ�糡����Ƭ�ͻ������е���Ρ�ͬʱ�����е�α��ֻ������Ӧ�Ľ����ѹ������������Ƶ���µ����������Ƶ�ʵ�������öࡣ��������ص㣬Ϊ�˵õ��͵������ѹ�Ͷ̵�����ʱ�䣬�ھ�������ʩ�ӵĽ����ѹ��Ƶ������Ӧ��Ҫ�����ھ��������Ƶ�ʸ�����

��ͼ2 �����Ч��·

��ͼ2 �����Ч��·��һ������£���Ƭ��е������ͽ���糡������dz�С��������ӽ����ѹ��Ƶ��Ϊijһ�ض�ֵʱ��������ԼӴ�����Ƶ���µ������ö࣬���������Ϊѹ��г��ʯӢ���������ĵ�Ч��·��ͼ2��ʾ������ʯӢ������ɲ���г���·ʱ���������Ϊ���ԣ����ЧƷ������Qֵ�ܸߡ���Ч�迹Ƶ��������ͼ3��ʾ��

��ͼ3 �����Ч�迹

��ͼ3 �����Ч�迹ͼ3�У�FrΪ����г��㡣��Ƶ��ΪFr = 1/(2�С�LC)ʱ��ͼ2�д�����L��Cг����֧·��ЧΪһ�������衣FaΪ����г��㣬��ʱ����֧·��ЧΪ��У��벢����C0г��Fa= Fr��1+C/C0����ʱ��Ч�迹���������ͨ��������Ƶ�ʵ�֮��IJ�ֵ��С���ܵ���˵��������Ϊ�����ڴ���г��ʱ����Ϊ���裬�ڲ���г��ʱ����Ϊ��С����ィ�����ʱ���ò���г�繤ѧ���������������г��㣬��Ƶ�ʵĸߵͷ����нϵ͵�Ƶ���Ǵ���г�ϸߵ�Ƶ���Dz���г��

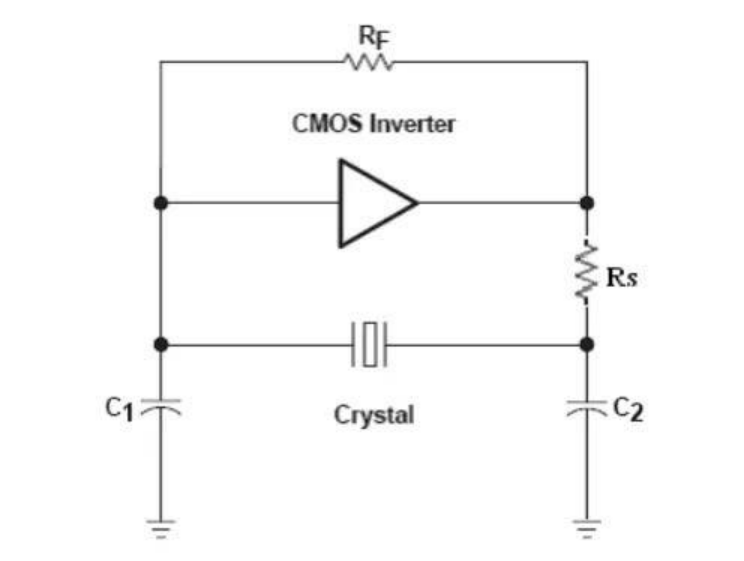

Ƥ��˹������������Ϊ�Ŵ�����ͬʱ�ṩ180�ȵ����ơ��������������Ϊ������·���ṩʣ�µ�180�����ơ�RFΪ�������裬����������������ֱ�������㣬ʹ֮�����ڸ�������(������)���������ֵ����̫С������ᵼ�»�·�����õ�·���þ���IJ���г�����ڲ���г����C0�йأ����ܼ�������Ӱ�죬������Ӹ��ص���C1��C2���ɼ�СC0��г��Ƶ�ʵ�Ӱ�졣ͬʱC1��C2�ļ����Ӱ������ʱ�����Ƶ�ʵ�ȷ�ȡ����ص��ݵ�ѡ��Ӧ���ݾ���Ӧ���ṩ��datasheet����ֵѡ�������ɷ�Χ�ڣ����ص���ֵԽ��Խ�á���ֵƫ�����������������ȶ�����������������ʱ�䡣

��ͼ4 Ƥ��˹������·

��ͼ4 Ƥ��˹������·Rs�������Ƹߴ�г�����Ӷ�ʹ������ý�Ϊ������Ƶ�ס�Rs��ֵ��̫С�Ļ������ܻᵼ�¾���Ĺ�������(overdrive)�����¾������������̡�ͨ��ȡRs=XC2��Rs��Ӱ���������ͼ������

��ͼ5 Rs��Ӱ�죨���Բο����ϣ�

��ͼ5 Rs��Ӱ�죨���Բο����ϣ���·�����ͼ6��PM0��NM0���ɵ���������Ƭ���·��ͬ�����·��PM7~PM9��NM7~NM9���ʩ���ش��������Բ��ν������κͷŴ�����ź��پ�����������������������������������

��ͼ6 xtal��·ԭ��ͼ

��ͼ6 xtal��·ԭ��ͼ��������ʾRsС��ʱ����ͬ���ļ�����ѹ�£����η��ȱ�Rs������С�ܶ࣬����XC���Ϊһ��ֱ�ߡ�

��XOUT

��ͼ7 XOUT��XC�IJ���ͼ

��ͼ7 XOUT��XC�IJ���ͼ�������ע�������ڵ�������о����ѡ��dz���Ҫ���������˯���ѵ�ϵͳ������ʹ�õ͵�ѹ������ġ����ڵ����ѹʹ�ṩ������ļ������ʼ��٣���ɾ����������������Ͳ���������һ�������ϵ縴λʱ�����ر����ԣ��ϵ�ʱ��·���㹻���Ŷ���������������˯����ʱ����·���Ŷ�Ҫ���ϵ�ʱС�ö࣬�����úܲ����ס�����·�У�����Ȳ��ܹ�����(�����ߴ�г����)Ҳ����Ƿ����(����������)��

�����ѡ��Ӧ�������¼���Ҫ�أ�г��Ƶ�㡢���ص��ݡ��������ʡ��¶����ԡ������ȶ��ԡ����仰˵������ɿ��Թ��������ܵ����ص��ݵ�Ӱ�졣���ڸ��ص��ݵ�ѡ��Ӧ���ݾ���Ӧ���ṩ��datasheet����ֵѡ�������ɷ�Χ�ڣ����ص���ֵԽ��Խ�á���ֵƫ�����������������ȶ�����������������ʱ�䡣�еľ����Ƽ���·������Ҫ��������RS����һ����������ֹ������������������������ὥ����ļ��پ���ĽӴ���ƣ��⽫����Ƶ�ʵ����������Ƶ��ƫ�ƣ������ϻ���

��ƾ����ܽ�01����Ҫѡ��һ���͵ĵ�Ч��������ľ��塣���崮������������ڽ����������⡣��Ϊ�͵ľ����Ч��ֵ���������ӻ�·���档

02ͨ������ӡ�Ƶ�·�������������ͼ������ݡ��Ӷ������������������;���Ƶ���ȶ��ȵ����⡣

03Ӧ�ñ��ֶԾ���Ӧ���¶Ⱥ͵�ѹ��Χ���ּ�أ��Ӷ����־�������Ƶ���б�Ҫ�Ļ�Ҫ�������ݵ����ֵ��

04��Ҫ�õ����Ч�����������Ӧ�ò���Vdd���ֵ������40%��Ϊ����ʱ�ӷ������������źš��������ھ��������Dz��ܴﵽ��һҪ��ġ�����Ҳ���Բο����������̵�ʹ��˵������ù��ھ�����ƽ�һ���İ�����

05�����Ƽ����Ż���R1����ֵ���������õ������ȼ������C1��C2��ֵ��Ȼ����R1��λ��������һ����λ�ƣ�����λ�Ƶij�ʼֵ����ΪXC1����������ͨ�����ڵ�λ������֤������Ҫ��Ƶ���������Լ�ά�־�����̬��