imec首次展示CFET晶体管,将在0.7nm A7节点引入

2024年06月21日 08:57 发布者:eechina

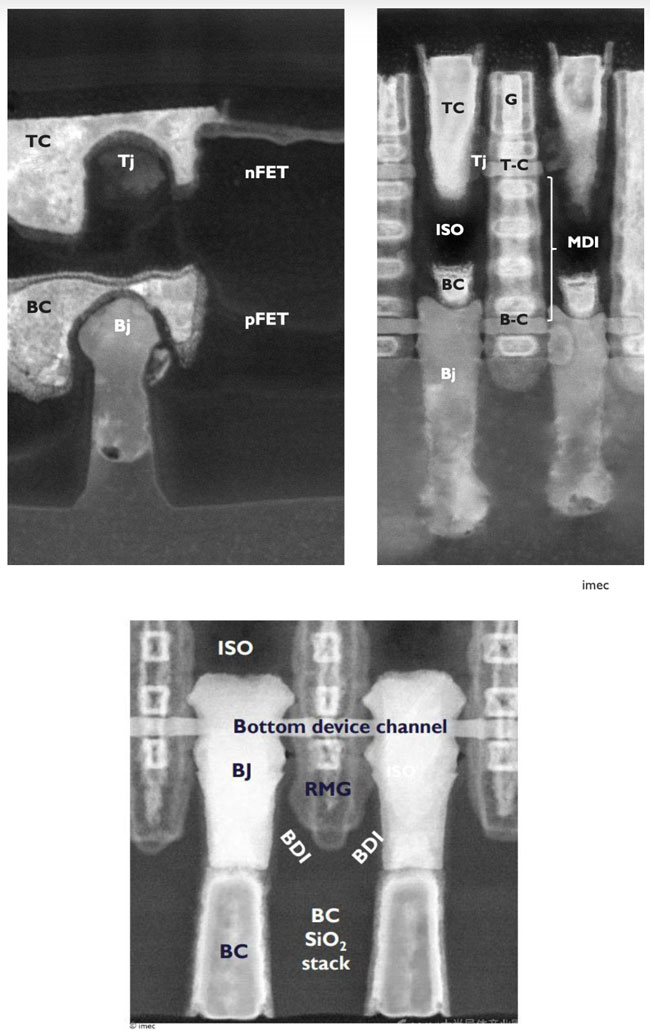

来源:大半导体产业网自比利时微电子研究中心(imec)官网获悉,6月18日,在2024 IEEE VLSI技术与电路研讨会(2024 VLSI)上,imec首次展示了具有堆叠底部和顶部源极/漏极触点的CMOS CFET器件。虽然这一成果的两个触点都是利用正面光刻技术获得,但imec也展示了将底部触点转移至晶圆背面的可能性――这样可将顶部元件的覆盖率从11%提升至79%。

从imec的逻辑技术路线图看,其设想在A7节点器件架构中引入CFET技术。若与先进的布线技术相辅相成,CFET有望将标准单元高度从5T降低到4T甚至更低,而不会降低性能。在集成nMOS和pMOS垂直堆叠结构的不同方法中,与现有的纳米片工艺流程相比,单片集成被认为是破坏性最小的。

imec在研讨会上首次展示的具有顶部和底部触点的功能单片CMOS CFET器件,栅极长度为18nm,栅极间距为60nm,n型和p型之间的垂直间距为50nm。

imec负责人表示,在从正面开发底部触点时,遇到了很多挑战,可能影响底部触点电阻,并限制顶部器件工艺窗口。在2024 VLSI上,imec表明,尽管仍使用晶圆键合和减薄等额外工艺,这一设计是可行的,这使得晶圆背面底部接触结构成为对业界来说具有强大吸引力的选择。目前,该机构正在持续进行研究,以确定最佳的触点布线方法。