下一代CFET晶体管密度翻倍 英特尔、台积电和三星展示各自方案

2023年12月21日 15:28 发布者:eechina

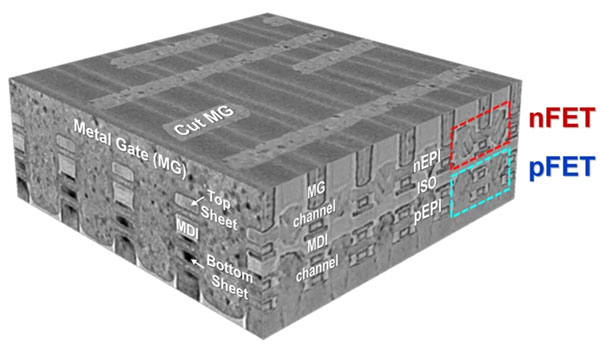

来源:EXPreview在上周的IEEE IEDM会议上,英特尔、台积电(TSMC)和三星展示了各自的CFET晶体管方案。堆叠式CFET架构晶体管是将n和p两种MOS器件相互堆叠在一起,未来将取代GAA(Gate-All-Round),成为新一代晶体管设计,以实现密度翻倍。

英特尔是首个展示CFET方案的晶圆代工厂,早在2020年就公开了首个早期版本。这次英特尔介绍了CFET制造的最简单电路之一,即反相器的几项改进。CMOS反相器将相同的输入电压发送到堆栈中两个设备的栅,并产生一个逻辑上与输入相反的输出,而且反相器在一个鳍上完成。英特尔同时还将晶体管使用的纳米片数量从2个增加到3个,垂直间隙也从50nm减小到30nm。

目前5nm制程节点的栅极间距为50nm,不过这是使用单侧互连的简单FinFET。三星展示的CFET方案里,栅极间距为45/48nm,比起英特尔的60nm要更小。尽管三星的CFET原型里45nm栅极间距版本性能有所下降,但研究人员认为通过对制造过程的优化可以解决这个问题。三星成功之处是能够电气隔离堆叠的n和p两种MOS器件的源和漏,关键步骤是使用一种涉及湿化学品的新型干刻蚀来替代湿法刻蚀。另外与英特尔单个晶体管使用3个纳米片不同,三星是成对晶体管使用单个纳米片。

台积电与三星一样,设法将栅极间距控制在48nm,其CFET方案的特点包括一种在顶部和底部晶体管之间形成介电层的新方法,以保持间距。纳米片通常由硅和硅锗的交替层形成,台积电尝试使用硅锗专用刻蚀方法,在释放硅纳米线之前于两个晶体管之间构建隔离层。

据了解,CFET技术转化为商业大规模使用大概还需要7到10年的时间,在此之前仍然有许多前期准备工作要完成。