基于Xines广州星嵌OMAPL138 DSP+ARM+FPGA无人机避障系统

2023年09月18日 21:53 发布者:CoreKernel

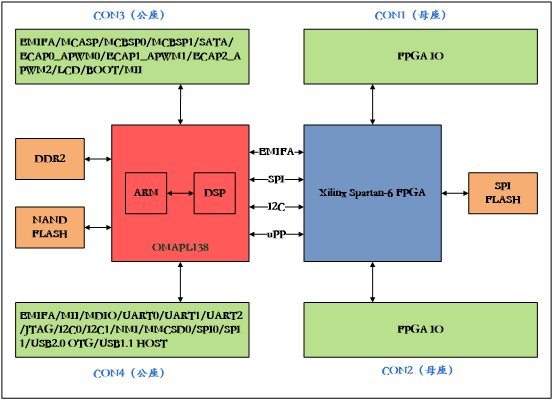

基于Xines广州星嵌OMAPL138 DSP+ARM+FPAGA硬件平台、毫米波雷达平台以及大疆的无人机平台,开发了一套将毫米波雷达与单目视觉相融合的无人机自主避障演示系统;并利用该无人机自主避障演示系统做了避障飞行实验,初步验证了融合方案在无人机自主避障飞行中的可行性。  框架解析: 前端由Xilinx Spartan-6 XC6SLX16/45 FPGA采集AD数据,AD数据通过uPP或者EMIF总线传输至OMAP-L138的DSP。 数据被DSP处理之后,通过DSPLINK或者SYSLINK双核通信组件被送往ARM,用于应用界面开发、网络转发、SATA硬盘存储等应用。OMAP-L138的DSP或者ARM根据处理结果,将得到的逻辑控制命令送往FPGA,由FPGA控制板载DA实现逻辑输出。(1) 高速数据采集前端部分由Xilinx Spartan-6 XC6SLX16/45 FPGA同步采集AD模拟输入信号,可实现对AD数据进行预滤波处理,另外一路DAC可输出任意幅值和任意波形的并行DA数据。(2) 高速数据传输部分由uPP、EMIF、SPI和I2C通信总线构成。大规模吞吐量的AD和DA数据,可通过uPP总线在DSP和FPGA之间进行高速稳定传输;DSP可通过EMIF总线对FPGA进行并行逻辑控制和进行中等规模吞吐量的数据交换;ARM可通过SPI和I2C对FPGA端进行初始化设置和参数配置。(3) 高速数据处理部分由DSP核和算法库构成。可实现对AD和DA数据进行时域、频域、幅值等信号参数进行实时变换处理(如FFT变换、FIR滤波等)。(4) DSP+ARM双核通信部分由DSP核、ARM核和DSPLINK/SYSLINK双核通信组件构成。通过内存共享方式,实现DSP和ARM双核之间的数据交换和通信。(5) 数据显示存储拓展部分由ARM核、图形显示、网络和SATA硬盘等部分构成。通过ARM的应用界面可实时显示AD和DA的时域和频域波形;并可实现大数据存储和远程网络通信。 1.1.1 OMAP-L138+FPGA评估板资源图

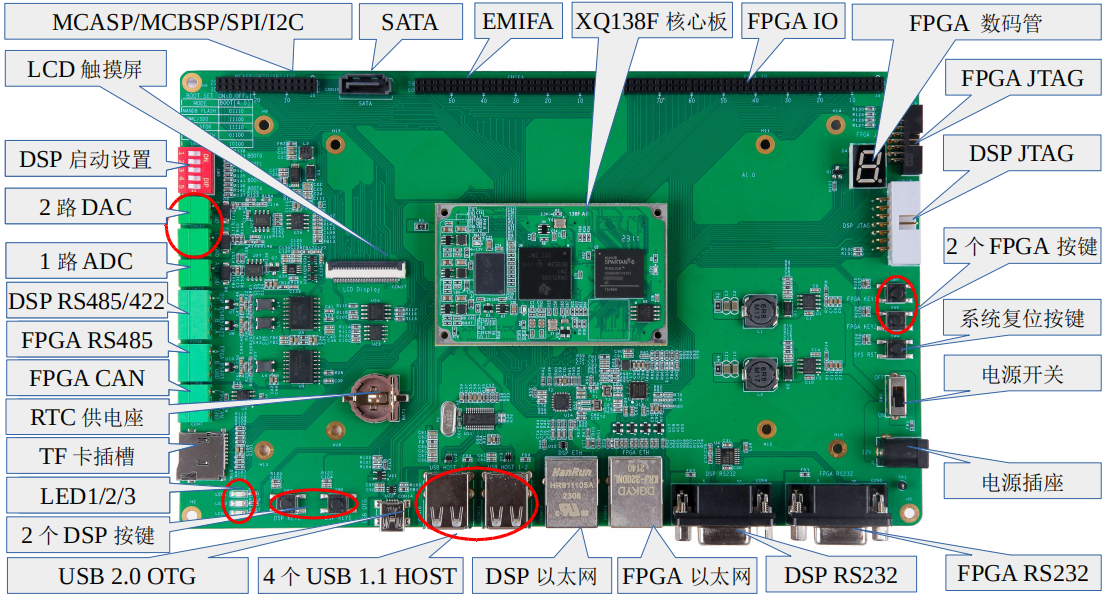

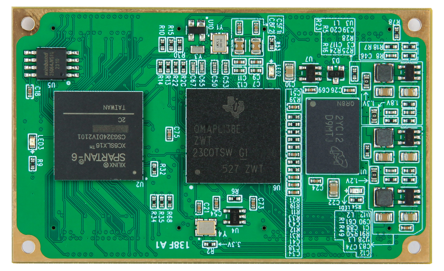

框架解析: 前端由Xilinx Spartan-6 XC6SLX16/45 FPGA采集AD数据,AD数据通过uPP或者EMIF总线传输至OMAP-L138的DSP。 数据被DSP处理之后,通过DSPLINK或者SYSLINK双核通信组件被送往ARM,用于应用界面开发、网络转发、SATA硬盘存储等应用。OMAP-L138的DSP或者ARM根据处理结果,将得到的逻辑控制命令送往FPGA,由FPGA控制板载DA实现逻辑输出。(1) 高速数据采集前端部分由Xilinx Spartan-6 XC6SLX16/45 FPGA同步采集AD模拟输入信号,可实现对AD数据进行预滤波处理,另外一路DAC可输出任意幅值和任意波形的并行DA数据。(2) 高速数据传输部分由uPP、EMIF、SPI和I2C通信总线构成。大规模吞吐量的AD和DA数据,可通过uPP总线在DSP和FPGA之间进行高速稳定传输;DSP可通过EMIF总线对FPGA进行并行逻辑控制和进行中等规模吞吐量的数据交换;ARM可通过SPI和I2C对FPGA端进行初始化设置和参数配置。(3) 高速数据处理部分由DSP核和算法库构成。可实现对AD和DA数据进行时域、频域、幅值等信号参数进行实时变换处理(如FFT变换、FIR滤波等)。(4) DSP+ARM双核通信部分由DSP核、ARM核和DSPLINK/SYSLINK双核通信组件构成。通过内存共享方式,实现DSP和ARM双核之间的数据交换和通信。(5) 数据显示存储拓展部分由ARM核、图形显示、网络和SATA硬盘等部分构成。通过ARM的应用界面可实时显示AD和DA的时域和频域波形;并可实现大数据存储和远程网络通信。 1.1.1 OMAP-L138+FPGA评估板资源图  图4 OMAP-L138+FPGA三核高速数据采集处理资源图 1.1.2 评估板简介基于TI OMAP-L138(定点/浮点 DSP C674x+ARM9)+ Xilinx Spartan-6 FPGA处理器; OMAP-L138 FPGA 通过uPP、EMIFA、I2C总线连接,通信速度可高达 228MByte/s; OMAP-L138主频456MHz,高达3648MIPS和2746MFLOPS的运算能力; FPGA标配为Spartan-6系列芯片XC6SL16,可升级至XC6SL45; 开发板引出丰富的外设,包含SATA、SD、USB OTG、USB HOST、UART、双网络(1个千兆FPGA端、1个百兆DSP端)、ADC、DAC、DSP RS485/422、FPGA RS485、FPGA CAN、DSP RS232、FPGA RS232、RTC、LCD,引出了MCASP、MCBSP、uPP、 SPI、 EMIFA、 I2C等接口,方便用户扩展。 DSP+ARM+FPGA三核核心板,尺寸为 72mm*44mm,采用工业级B2B连接器,保证信号完整性; 支持裸机、SYS/BIOS 操作系统、Linux 操作系统。

图4 OMAP-L138+FPGA三核高速数据采集处理资源图 1.1.2 评估板简介基于TI OMAP-L138(定点/浮点 DSP C674x+ARM9)+ Xilinx Spartan-6 FPGA处理器; OMAP-L138 FPGA 通过uPP、EMIFA、I2C总线连接,通信速度可高达 228MByte/s; OMAP-L138主频456MHz,高达3648MIPS和2746MFLOPS的运算能力; FPGA标配为Spartan-6系列芯片XC6SL16,可升级至XC6SL45; 开发板引出丰富的外设,包含SATA、SD、USB OTG、USB HOST、UART、双网络(1个千兆FPGA端、1个百兆DSP端)、ADC、DAC、DSP RS485/422、FPGA RS485、FPGA CAN、DSP RS232、FPGA RS232、RTC、LCD,引出了MCASP、MCBSP、uPP、 SPI、 EMIFA、 I2C等接口,方便用户扩展。 DSP+ARM+FPGA三核核心板,尺寸为 72mm*44mm,采用工业级B2B连接器,保证信号完整性; 支持裸机、SYS/BIOS 操作系统、Linux 操作系统。 图1 开发板正面图

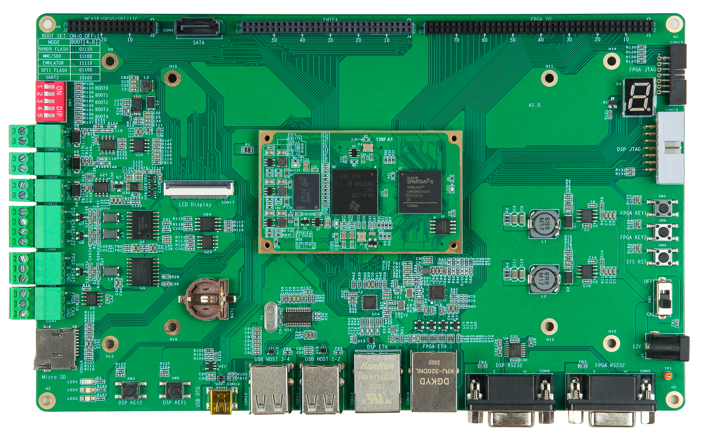

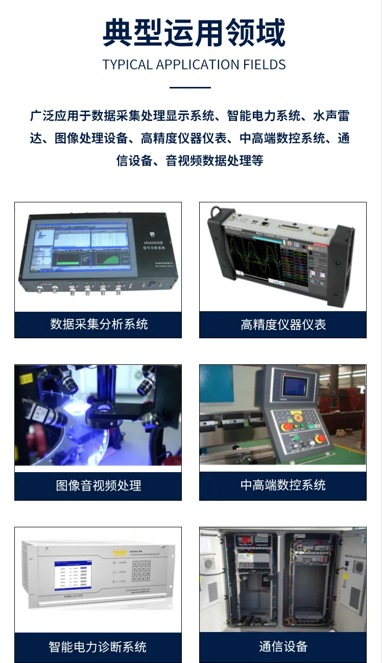

图1 开发板正面图  图2 开发板侧视图 XQ138F-EVM是一款基于广州星嵌SOM-XQ138F核心板设计的开发板,采用沉金无铅工艺的4层板设计,它为用户提供了 SOM-XQ138F核心板的测试平台,用于快速评估SOM-XQ138F核心板的整体性能。 SOM-XQ138F核心板采用沉金无铅工艺的8层板设计,引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层应用,大大降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。不仅提供丰富的 Demo 程序,还提供详细的开发教程,全面的技术支持,协助客户进行底板设计、调试以及软件开发。1.1.3 典型运用领域数据采集处理显示系统智能电力系统图像处理设备高精度仪器仪表中高端数控系统通信设备音视频数据处理

图2 开发板侧视图 XQ138F-EVM是一款基于广州星嵌SOM-XQ138F核心板设计的开发板,采用沉金无铅工艺的4层板设计,它为用户提供了 SOM-XQ138F核心板的测试平台,用于快速评估SOM-XQ138F核心板的整体性能。 SOM-XQ138F核心板采用沉金无铅工艺的8层板设计,引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层应用,大大降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。不仅提供丰富的 Demo 程序,还提供详细的开发教程,全面的技术支持,协助客户进行底板设计、调试以及软件开发。1.1.3 典型运用领域数据采集处理显示系统智能电力系统图像处理设备高精度仪器仪表中高端数控系统通信设备音视频数据处理 图3 典型应用领域1.1.4 OMAP-L138+FPGA评估板简介 广州星嵌设计的XQ138F-EVM是一款DSP+ARM+FPGA三核高速数据采集处理开发板,适用于电力、通信、工控、医疗和音视频等数据采集处理领域。 此设计采用OMAP-L138+Spartan-6平台,其中OMAP-L138是德州仪器(TI)低功耗高性能浮点DSP C6748+ARM9双核处理器,而Spartan-6是赛灵思(Xilinx)平台升级灵活、性价比极高的FPGA处理器。此设计通过OMAP-L138的uPP、EMIF等通信接口将两个芯片结合在一起,而OMAP-L138内部的DSP和ARM通过DSPLINK/SYSLINK进行双核通信,实现了需求独特、灵活、功能强大的DSP+ARM+FPGA三核高速数据采集处理系统。 1.1.5 Xilinx Spartan-6 FPGA和TI OMAP-L138通信实现

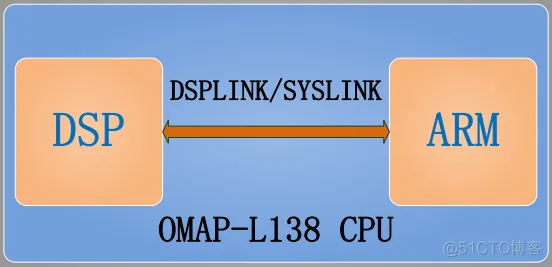

图3 典型应用领域1.1.4 OMAP-L138+FPGA评估板简介 广州星嵌设计的XQ138F-EVM是一款DSP+ARM+FPGA三核高速数据采集处理开发板,适用于电力、通信、工控、医疗和音视频等数据采集处理领域。 此设计采用OMAP-L138+Spartan-6平台,其中OMAP-L138是德州仪器(TI)低功耗高性能浮点DSP C6748+ARM9双核处理器,而Spartan-6是赛灵思(Xilinx)平台升级灵活、性价比极高的FPGA处理器。此设计通过OMAP-L138的uPP、EMIF等通信接口将两个芯片结合在一起,而OMAP-L138内部的DSP和ARM通过DSPLINK/SYSLINK进行双核通信,实现了需求独特、灵活、功能强大的DSP+ARM+FPGA三核高速数据采集处理系统。 1.1.5 Xilinx Spartan-6 FPGA和TI OMAP-L138通信实现  图5 FPGA与OMAP-L138通信框图

图5 FPGA与OMAP-L138通信框图  图6 OMAP-L138+FPGA核心板 高速通信总线――uPP uPP(Universal Parallel Port)是OMAP-L138 CPU颇具特色的高速并行数据传输总线,可以单独发送和接受数据,也可以同时接收和发送数据,常用于和FPGA以及其他并口设备数据传输。 OMAP-L138的uPP 共有2个通道(通道A和通道B),共有32位数据线,控制简单,配置灵活,数据吞吐量大。uPP时钟速率可高达处理器时钟速率的一半,对于在456MHz下运行的OMAP-L138处理器,uPP单通道吞吐量理论值可高达228MB/s。 1.1.6 TI OMAP-L138的DSP和ARM双核通信实现

图6 OMAP-L138+FPGA核心板 高速通信总线――uPP uPP(Universal Parallel Port)是OMAP-L138 CPU颇具特色的高速并行数据传输总线,可以单独发送和接受数据,也可以同时接收和发送数据,常用于和FPGA以及其他并口设备数据传输。 OMAP-L138的uPP 共有2个通道(通道A和通道B),共有32位数据线,控制简单,配置灵活,数据吞吐量大。uPP时钟速率可高达处理器时钟速率的一半,对于在456MHz下运行的OMAP-L138处理器,uPP单通道吞吐量理论值可高达228MB/s。 1.1.6 TI OMAP-L138的DSP和ARM双核通信实现 图6 OMAP-L138 DSP+ARM双核通信原理 基本原理 TI官方的DSPLINK/SYSLINK双核通信组件提供了一套通用的API,从应用层抽象出ARM与DSP的物理连接特性,从而降低用户开发程序的复杂度。其中DSPLINK使用DSP/BIOS操作系统,SYSLINK使用SYS/BIOS操作系统,SYSLINK属于DSPLINK的新版本双核通信组件。 在ARM和DSP的双核通信开发中,ARM端运行HLOS操作系统(一般是Linux),DSP端运行RTOS实时操作系统(一般是DSP/BIOS或者SYS/BIOS),双核主频456MHz。 优势(1) SOC片上DSP+ARM架构可实现稳定的双核通信,缩短了双核通信开发时间。(2) DSPLINK/SYSLINK双核通信组件突破了双核开发瓶颈,节约了研发成本。(3) SOC上的DSP和ARM架构简化了硬件设计,降低了产品功耗和硬件成本。

图6 OMAP-L138 DSP+ARM双核通信原理 基本原理 TI官方的DSPLINK/SYSLINK双核通信组件提供了一套通用的API,从应用层抽象出ARM与DSP的物理连接特性,从而降低用户开发程序的复杂度。其中DSPLINK使用DSP/BIOS操作系统,SYSLINK使用SYS/BIOS操作系统,SYSLINK属于DSPLINK的新版本双核通信组件。 在ARM和DSP的双核通信开发中,ARM端运行HLOS操作系统(一般是Linux),DSP端运行RTOS实时操作系统(一般是DSP/BIOS或者SYS/BIOS),双核主频456MHz。 优势(1) SOC片上DSP+ARM架构可实现稳定的双核通信,缩短了双核通信开发时间。(2) DSPLINK/SYSLINK双核通信组件突破了双核开发瓶颈,节约了研发成本。(3) SOC上的DSP和ARM架构简化了硬件设计,降低了产品功耗和硬件成本。