��-�� ADC�ĸ߾�����ģת���������ʵ�ֵģ����걾�ģ���Ͷ���

2023��05��09�� 10:53 �����ߣ�eechina

��Դ��Digi-Key���ߣ�Alan Yang

����ܻ�֪��Delta-Sigma(��-��) ADC���Դﵽ�ܸߵľ��ȣ����Ǿ�����ôʵ�ֵģ� ���Ľ�����������������ȡ��������ȸ������������Delta-Sigma ADC�Ĺ���ԭ����

��������ADC�Ļ�������

�������˽�Delta-Sigma (��-��) ADCԭ��֮ǰ������ȷ�������

1. ��������

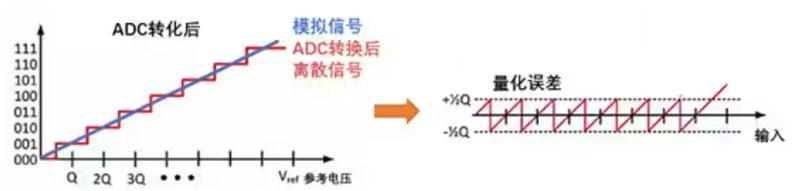

��ͼ�У���ɫб����������ģ���źţ�����״�����Ǿ���ADCת�������ɢ�źš�������ǰ���������������õ��ұ��Ǹ����ݲ�һ����������

ͼ1��������� ��ͼƬ��Դ��TI��

����������Quantization Noise��������Qֵ�����������������Խ�죬����Q֮��ľ���ԽС��Q�ķ�ֵԽ�ͣ�Ҳ�������������ķ�ֵԽ�͡���ȻQֵ��ֵ��ͣ���������Χ��������䡣��ˣ��ı�����ٶȣ����Ըı����������ķ�ֵ�������ܸı�������������������

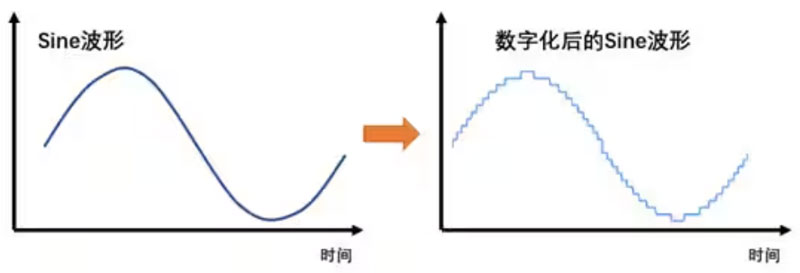

ͼ2�����ֻ����Sine���� ��ͼƬ��Դ��TI��

��ʱ���������һ��ģ���Sine���Σ�����ADCת�����ֻ������ǻ�õ����״��Sine���Ρ����Ǽӿ�����ٶȣ����Ѿ�ݱ�ú�ϸ���������ɴ��ڣ������������������������䡣

2. �����

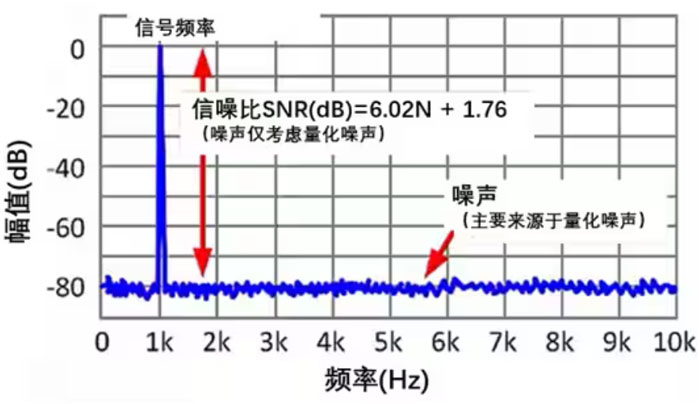

������ǰ������Sine���ηŵ�Ƶ���������ϣ���ź�Ƶ�ʵķ�ֵ������������ֵ����С��

ͼ3��Sine����Ƶ��Ӧ���ߣ�ͼƬ��Դ��TI��

��ͼ��������Ҫ��Դ������������ͨ������ȼ��㣬���ǻ�õ�һ���̶��Ĺ�ʽ��

�����SNR(dB)=6.02N + 1.76 ����������������������

SNR��ָ����������������ȣ�Signal noise ratio��

N��ָ����ADC����λ����������ǰ�N��ߣ��������ߣ����źŸ���������С������������ã���ˣ����ADC����λ����������߲���������

һ����˵����߲���λ����������ζ��ADC�ijɱ�����Ҳ����ߡ�

��û�в����λ����ͬ���Ż�����ȵķ����أ����ǡ��еġ����Ǿ��ǹ�������

3. ��������������

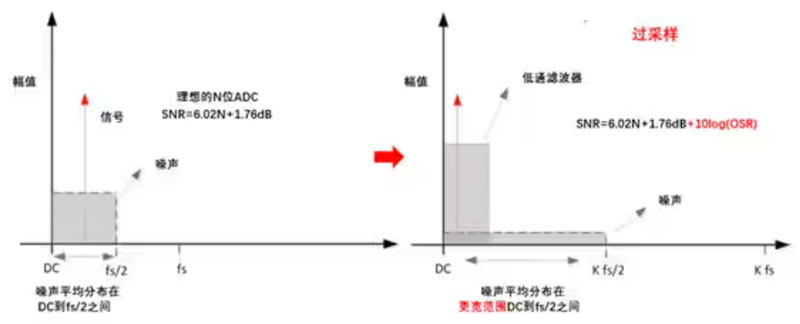

���ǰ�ͼ3��һ������ͼ��ɫ��ͷ��ʾ���źŵķ�ֵ����ɫ����������ֵ��ƽ���ֲ���DC��fs/2֮�䡣��fsΪ����Ƶ�ʣ�

ͼ4����������������

����ͼ��������ǽ����������K���������������䣬����ƽ���ֲ��ڸ�����Χ���Ӷ������ķ�ֵ���͡�ԭʼ�ź�û�䣬����������ֵ���٣�Ҳ�������������ˡ���߲�����֮�������ȹ�ʽ��

SNR=6.02N+1.76dB+10log(OSR)

���У�����������OSR =Fs/(2�wBW), BWΪ��������ע�⣺�˹�ʽ��������ֻ������������������ADC��

��ˣ���߲������������������ȡ�

С��ʿ�������Digi-Key��ѡ��Delta-Sigma (��-��) ADC

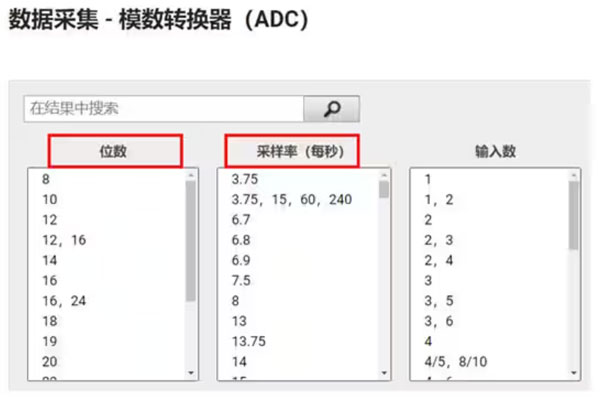

���ǿ�����Digi-Key��վ��ģ��ת������ADC�������£��ڼܹ�ѡ���ҵ������ǻ��֡�����Delta-Sigma ADC��

ͼ 5 Digi-Key ADC ����ɸѡ

����ͨ��������ɸѡADC������ͨ��ADC����λ���������ʵȹؼ�������ɸѡ���ʵ�ADC��

ͼ6����Digi-Key ��վ��ͨ������ɸѡ����ADC

Delta Sigma���Ƶ�ԭ��

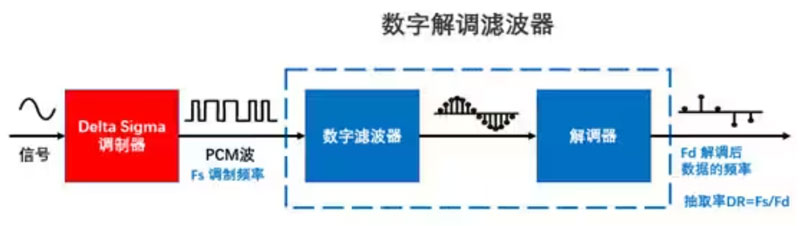

Delta Sigma���ƣ�����ģ���źŵ��Ƴɷ�����ʽ��PCM��Pulse Code Modulation���źš�PCM����һ��Ƶ�ʹ̶�ռ�ձȱ仯�IJ���ͨ���Ƚ��źź�Ƶ���Ʋ�������Ȼ�������˲�����ͨ��������õ�һ�����ֻ������ս����

ͼ7��Delta-Sigma (��-��) ADCԭ��

�������ֽ���˲������Ժ͵�����һ����Delta Sigma ADC���档Ҳ����Delta Sigma��������������һ�������ĵ���оƬ��Ȼ������ֽ���˲���������MCU�����TI C2000��

����Ĺ�����ʵ�Ǹ���һ�����ʶ��źŽ��г�ȡ����ȡ��DR=Fs/Fd��

�� FsΪ����Ƶ��

�� FdΪ������Ƶ��

�����ص㽲һ��Delta Sigma�������Ĺ���ԭ���������˲�����

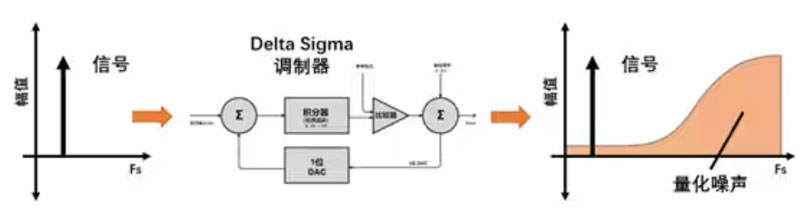

�� Delta Sigma�������Ĺ���ԭ��

ͨ��Delta Sigma���������ƣ����ǰ�ģ���źŵ��Ƴɷ�����ʽ��PCM�źš�

ͼ8��Delta-Sigma�����������ʱ��

��������һ�°�����ͼģ���źţ���ɫ���ߣ���PCM�źţ���ɫ����״�IJ��Σ����������ͬһ���źš�

ͼ 9 ��ģ���źš� VS ��PCM�źš�

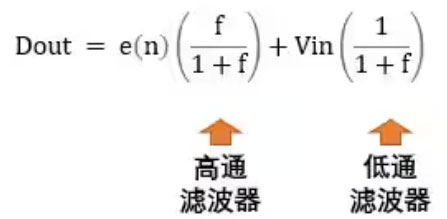

�� Delta Sigma���������ݺ���

ͼ10��Delta Sigma����������ͼ

ͨ������Ļ�·������Delta-Sigma���ֻ����ơ�

��·�Ĵ��ݺ���, ����������������֮��IJ�ֵ����ǰ��Ļ��ֻ��ڼ����������������ǿ��Եõ����ݺ�����

���������ݺ��������ǵõ����Dout

���ǿ��Կ�����(f/1+f) �������������൱��һ����ͨ�˲������� (1/1+f)���������ź��൱��һ����ͨ�˲�����

����Delta-Sigma���ƻ���֮��, �źű��Ż���������Ƶ��Χ�ڸ������⡣

��Ƶ�ʽϵ�ʱ���źű�����������������������Ƶ�ʱȽϸ�ʱ�����������������ź�������

ͼ11��Delta-Sigma �����������Ƶ��

��ˣ�ͨ��Delta-Sigma���ƻ���֮����Ч�ź�Ƶ��������Ƚ�һ�����Ż���

�� �����˲���

ͨ��Delta-Sigma ������֮�����ǻ���Ҫ��һ�������˲���

��ͼ�Ǿ���Delta Sigma������֮��ķ�Ƶ���ԣ�����������һ������ͼ������ʾ�������˲���������һ����ͨ�˲������Ѻ����ұߵĸ�Ƶ�����˳�����ôʣ�¾�����Ч���ź���Ϣ��

ͼ12�������˲���

�������˲����Ĵ�������Ƶ���ԣ����ǿ��Բ������߽���ȥ���ڡ�

���ֳ��������˲���������ʵ������Ҫ�ķ�Ƶ���ԣ�

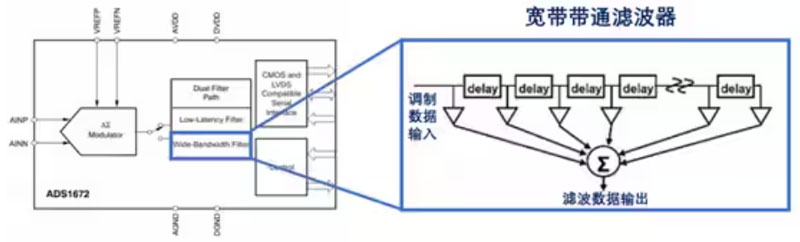

��������ͨ��һ��ʵ������˵����TI ADS1672оƬʹ����55��FIR (Finite Impulse Response��������������Ӧ)��ʵ���˿���ͨ���˲����Ĺ��ܣ�ͬʱ��ζ�ţ���Ҫ�ӳ�55��ʱ������������˲���

ͼ13��ADS1672���ÿ�����ͨ�˲���

һ����˵������Խ�ߣ���Ƶ����Խ�ã���������˥��Խ���������ǣ�����Խ�ߣ��������ӳ�ҲԽ�����ԣ��ڸ��õķ�Ƶ���Ի���Ҫ�������Ӧ����ʱ���Dz��ò�ȡ�ᡣ

С��ʿ��TI ADS1672��Ӧ������ADS1672EVM-PDK

ͼ14��������ADS1672EVM-PDK

ADS1672EVM-PDK ��24λ ��78.1k ~ 625k�����ʣ�����ADC��������ADCPro™�����÷������ߣ�����ʾ������FFT��ֱ��ͼ��ʾ�ȣ������ʡ���ʱ�䡣

������

Delta-Sigma (��-��) ADC���Դﵽ�ܸߵľ��ȣ���Ҫ�������������˲����������������Ӷ�ʵ�ָ߷ֱ��ʡ����������Ĵ����������˲����ٶȣ��ӳٱ����Ҳ��С���������������ԣ�Delta-Sigma (��-��) ADC�������źŲɼ����߾��Ȳ������������Ź㷺��Ӧ�á�