实现高性能的数据中心和工业系统可编程时钟发生器

2023年04月17日 10:29 发布者:eechina

来源:Digi-Key在设计服务器、存储系统和网络或嵌入式工业系统时,精确定时对于支持以太网和外设快速互连标准 (PCIe) 通信至关重要,并且可能会带来挑战。这不仅仅是要添加一条以太网或一条 PCIe 总线的问题。典型的设计可能包含多条总线,所有这些总线都需要最小抖动的精确定时支持。典型的系统需要混用不同的通信总线,这些总线在各种频率下运行,最高可达 650 MHz。

因此,您需要尽可能少占用印刷电路板 (pc) 空间的解决方案。此外,以太网与 PCIe 的定时需求各异,这增加了设计难度。为了满足这些需求,您可以使用紧凑型可编程时钟发生器 IC,这类 IC 可以同时为以太网和 PCIe 总线提供多达 12 个参考时钟。

这篇博客简要介绍了以太网和 PCIe 总线的部分定时需求,然后展示了来自 Renesas 的紧凑型可编程时钟发生器解决方案,该解决方案能同时满足多条 PCIe 和以太网总线的需求。此外,博客中还介绍了可加速开发服务器、存储系统和网络或嵌入式工业系统中所用定时电路的评估板。

控制抖动和最大限度地减少 EMI

PCIe 和以太网具有不同的用途。PCIe 应用包括 PC 板上的芯片到芯片通信和扩展卡连接,而以太网则用于局域网 (LAN)、存储区域网络 (SAN) 和类似应用。不同的操作环境对定时电路的需求各不相同。

抖动衰减在以太网网络中至关重要。例如,在频率高达 650 MHz 的高速以太网中,均方根 (RMS) 相位抖动的上限需为 150 fs,方可确保信号完整性、低传播延迟,以及可预测的行为。

除了控制抖动外,PCIe 总线还受益于扩频调制的使用,此功能可将抖动能量分散至更宽频率,从而最大限度地减少电磁干扰 (EMI)。控制 EMI 意味着对 PC 板的屏蔽要求降低,这可缩减系统成本并加快系统集成。Renesas VersaClock 发生器让您可以控制扩频调制量,以优化特定应用所需的成本性能权衡。

用更少空间做更多事

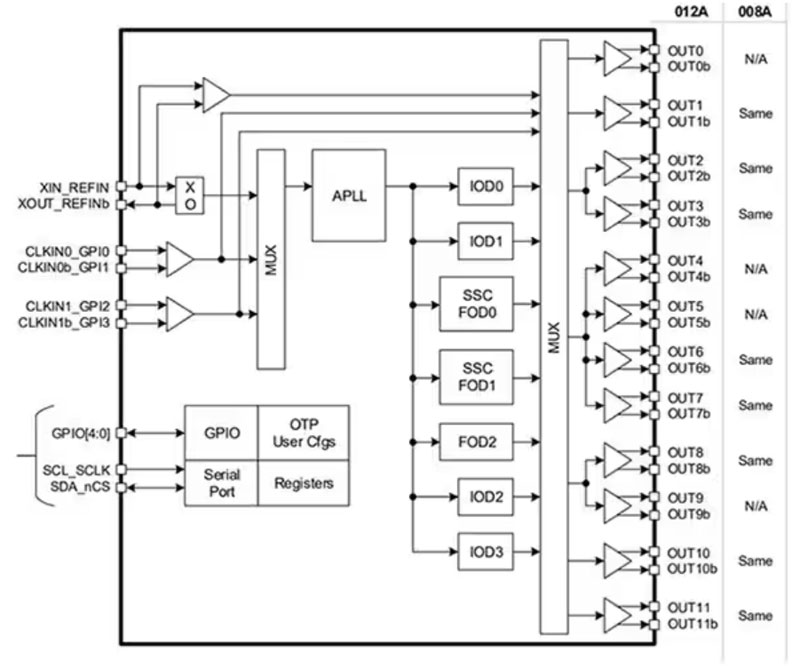

基于 Renesas VersaClock 发生器的集成定时解决方案有助于在更少的 PC 板空间内做更多事。这种解决方案配备 8 个或 12 个独立时钟,并且具有以下特性(图 1):

· 相位抖动:169 fs RMS(10 kHz-20 MHz,156.25 MHz)

· PCIe Gen6 公共时钟 (CC) 27 fs RMS

· 支持 PCIe 单独参考独立扩频 (SRIS) 和单独参考无扩频 (SRNS) 操作

· 1 kHz 到 650 MHz 低压差分信号 (LVDS) 和低功耗高速电流导引逻辑 (LP-HCSL) 输出

图 1:VersaClock 可编程时钟发生器可支持多达 8 个时钟(右侧的“008A”列)或 12 个时钟(“012A”列)。(图片来源:Renesas)

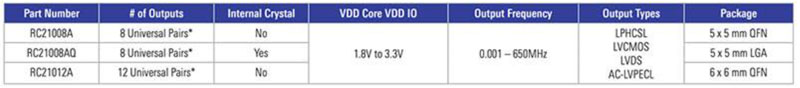

采用 5 个独立时钟构建定时解决方案的传统方法需要一个共用晶体振荡器电路(占用约 3 x 3 mm 的电路板空间),以及 4 个子振荡器(每个约占用 5 x 3 mm 的空间)。或者,您可以使用单个 VersaClock IC,如仅占据 5 x 5 mm 空间的 RC21008A。同样的 IC 可以支持多达 8 个时钟输出,进一步减少了板空间、元器件数和成本。下方展示了 RC21008A 的关键特性,以及来自 VersaClock 7 系列的两款其他 IC:RC21008AQ 和 RC21012A(表 1)。

表 1:VersaClock 7 系列中 3 个时钟发生器的关键特性;“*”表示输出可配置为差分或 LVCMOS。(表来源:Renesas)

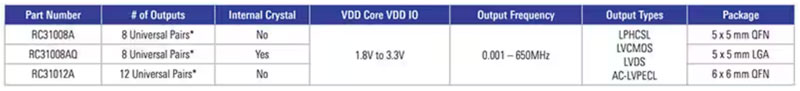

衰减抖动

RC31008A、RC31008AQ 和 RC31012A 可编程抖动衰减器具有网络同步功能,包括用于转换器同步的 JEDEC JESD204B/C 接口,支持 AC 或 DC 耦合的单端或差分输出,以及支持用于网络同步的同步以太网 (SyncE)。与 VersaClock 时钟发生器 IC 类似,这些抖动衰减器提供 8 个或 12 个输出,可以减少解决方案的尺寸和成本(表 2)。

表 2:VersaClock 7 系列中的抖动衰减器,“*”表示可配置为差分或 LVCMOS 的输出数。(表数据:Renesas)

评估板

为了加速您的开发活动,Renesas 提供了一系列评估板 (EVB),其中包括分别用于 8 输出和 12 输出时钟发生器设计的 RC21008-EVB(图 2)和 RC21012-EVB,以及分别用于 8 输出和 12 输出抖动衰减器的 RC31008-EVB 和 RC31012-EVB 评估板。这些评估板可以支持在合成器模式下生成时钟,以符合 PCIe 标准并实现扩频性能,它们还支持抖动衰减模式。在差分模式下,这些评估板支持的参考输入频率范围为 1 kHz 到 650 MHz;在单端模式下则为 1 kHz 到 200 MHz。它们的典型功率耗散低于 1 W,抖动规格为:

· 150 fs RMS 相位抖动(12kHz–20MHz,整数)

· 200 fs RMS 相位抖动(12kHz–20MHz,分数)

图 2:适用于 VersaClock 7 系列的 RC21008-EVB 等评估板支持开发 8 输出解决方案。(图片来源:Renesas)

结语

综上所述,来自 Renesas 的 VersaClock 时钟发生器和抖动衰减器可用于为各种数据处理和工业应用中的 PCIe 和以太网总线开发高性能、低成本的紧凑型定时解决方案。为了帮助您启动工作,厂家提供了评估板来加快开发进程并缩短上市所需时间。