Microchip FPGA 如何利用 HLS 提高使用 C++的电机控制应用的生产率

2022年06月16日 10:42 发布者:eechina

作者:Microchip Technology Inc. 资深市场营销工程师 Apurva Peri使用 SmartHLS™可将开发时间缩短最多 5 倍。

高级电机控制应用简介

现今的电机控制应用需要具有明确结果的多轴、多功能解决方案。试想一下大型自动化工业制造单元中的机器人(循环执行任务),甚至是机器人辅助进行的医疗手术――这些机器人需要在各个方向上精确控制,同时产生确定性输出。同样,高端工业级无人机需要稳定的陀螺仪和更高的机械可靠性,以及 DSP 的高速计算能力。在更重要的场景中,例如植入像心室辅助装置这样的医疗植入体(改善心脏功能),这类操作不容有任何闪失,因此除了精度和确定性之外,稳健性和可靠性也必不可少。电动机还执行诸如航天器中的姿态控制、展开机制、运动和节流阀控制等关键功能。机翼执行机构通常在起飞后或准备着陆时以较低的速度维持飞机的燃油效率。这些应用需要在高真空、辐射和不断变化的工作环境下保持较长的使用寿命、高可靠性和安全性。

降低系统成本,打造将数字外设与处理器内核集成在一起的单一联网、多协议硬件,是一以贯之的需求。

FPGA 在电机控制设计中的优势

与 ASIC 相比,FPGA 的优势更多,最突出的一点是其具有现场可配置性的确定性并行计算功能。它们可以实现复杂的逻辑功能,支持多种系统的实现和修改。

我们的 FPGA 独树一帜,因为它们具有基于闪存的非易失性存储器。凭借这种瞬时启动技术,它们的功耗可比竞品 FPGA 低 30%到 50%。FPGA 具有抗辐射性能和独特的安全功能,例如避免过度构建和克隆、设计 IP 保护、信任根、安全数据通信和防篡改功能。具体而言,在电机控制方面,我们的 FPGA 具有低功耗、低抖动、低延迟、高精度、高确定性和可扩展性,可在解决现代电机控制应用面临的复杂挑战方面发挥重要作用。

SmartHLS 助力提高生产率

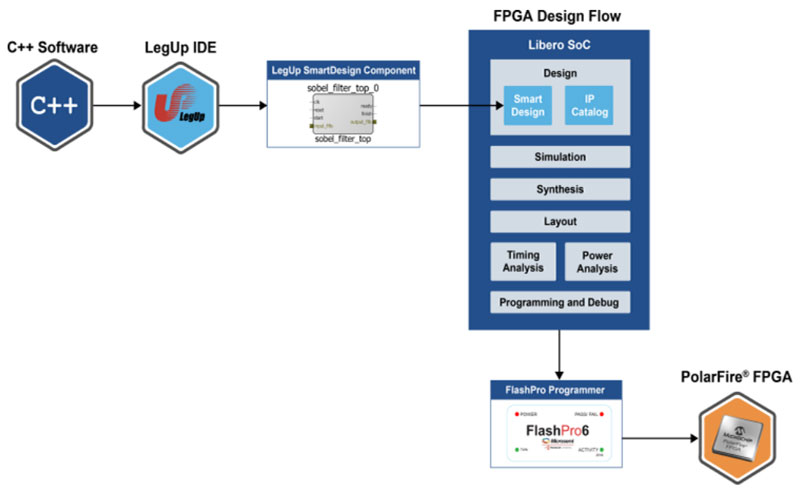

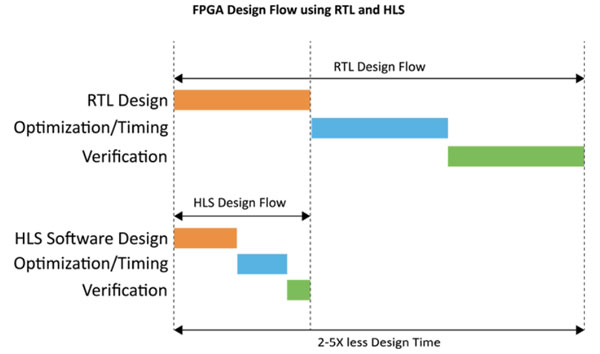

使用 Verilog/VHDL 从头开始为 FPGA 设计基于硬件的新电机控制器会非常耗时。通常,工程师已经有一个使用 C/C++设计的电机控制器正在运行。在这种情况下,理想的解决方案是针对 Microchip PolarFire® FPGA,自动将现有的 C++软件代码转换为等效的硬件实现。智能高级综合(SmartHLS™)工具和集成开发环境可使这项工作变得简单易行,它们可以针对 Microchip FPGA 将 C++软件编译成硬件模块。借助高级综合工具,您可以将 C++作为输入,并生成 Verilog 作为输出。通常,HLS 将生成的顶层 C++函数标记为等效的硬件 IP核心。您可以在顶层 C++函数中描述算法。然后,您可以使用 HLS pragma 和 C++ HLS 库来描述标准硬件接口,如 AXI、AXI-stream 或存储器接口。HLS 有一个颇具吸引力的好处,那就是与 RTL 设计相比,使用 C++可以显著提高抽象水平和生产率,这有助于缩短硬件设计和验证时间。HLS 可以轻松添加或删除流水线寄存器,以实现用户指定的目标频率,因此它非常适合进行架构探索。

我们有一位客户使用 SmartHLS 将其具有严格限制的高级电机控制设计移植到我们的FPGA。客户的主要目标是将确定性延迟时间缩短到 3 μs 以内。该延迟时间包括从接收每一个(共八个)电机编码器传感器的信号到 FPGA 电机控制内核更新所有这些传感器的电流输出之间的反馈时间。由于 DDR 和 PCIe®等外部 I/O 要求,客户还希望设计能够在 200MHz 以上的时钟频率下运行。此外,他们还希望能够将设计轻松安装到 PolarFire MPF500器件上。

客户给出了他们的结果质量报告,结果远超他们的设计目标。 他们的周期延迟时间缩短了 50%,同时频率提高到其目标时钟频率 200 MHz。电机控制器的最终确定性延迟时间也减半,缩短至约 2 μs。电机控制器的面积也缩小到足以放入 300K LE PolarFire FPGA。

将原始 C++电机控制器与经过改进的 FPGA 版本进行比较的实验表明,就延迟时间而言,基于 FPGA 的电机控制器的速度比 Arm®单片机高 2.5-6 倍,具体取决于单片机的抖动和实时操作系统。

单击此处了解有关 SmartHLS 的更多信息。

单击此处了解有关我们的电机控制解决方案的更多信息。

单击此处注册,可根据需要访问我们的网络研讨会“Microchip FPGA 如何利用 HLS 提高使用 C++的电机控制应用的生产率”