CTSD精密ADC―第4部分:轻松驱动ADC输入和基准电压源,简化信号链设计

2021年08月18日 16:22 发布者:eechina

作者:ADI公司 Abhilasha Kawle 和 Roberto Maurino本文重点介绍新型连续时间Sigma-Delta (CTSD)精密ADC最重要的架构特性之一:轻松驱动阻性输入和基准电压源。实现最佳信号链性能的关键是确保其与ADC接口时输入源或基准电压源本身不被破坏。使用传统ADC时,为实现输入和基准电压源与ADC的无缝接口,需要复杂的信号调理电路设计――称为前端设计。CTSD ADC的独特架构特性可简化并创新这种ADC与输入和基准电压源的接口。首先,我们快速回顾一下传统ADC的前端设计。

传统ADC的前端设计

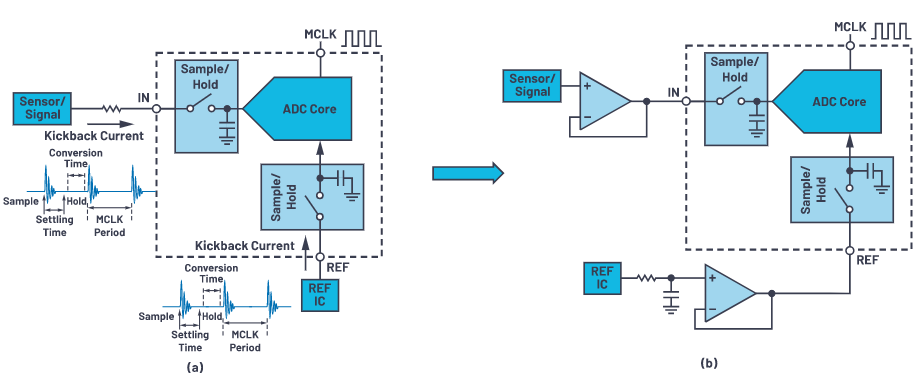

在本文中,"传感器"和"输入信号"可以互换使用,代表ADC信号链的任何类型的电压输入。ADC信号链的输入信号可以是传感器、来自某些源的信号或控制回路的反馈。众所周知,在传统的离散时间Sigma-Delta (DTSD) ADC和逐次逼近寄存器 (SAR) ADC中,输入和基准电压源处的采样网络是开关电容负载。当开关导通时,电容给输入充电;当开关断开时,电容保持采样值。在每个采样时钟边沿,当开关重新将电容连接到输入时,需要一个有限电流(称为反冲电流)来将电容充电或放电到新的采样值。该电流的曲线如图1a所示。大多数传感器和基准电压源IC无法驱动这种幅度的反冲电流,而如果直接与ADC接口,输入信号或基准电压源有很大可能遭到破坏。避免这种破坏的已知解决方案之一是使用驱动缓冲放大器将输入传感器和基准电压源与ADC隔离开来。驱动放大器应具有吸收这种反冲电流的能力,如图1b所示。这导致需要高压摆率和高带宽放大器来支持所需的输入充电/放电电流,并使反冲在一个采样时间周期内稳定下来。这些严格的要求限制了可用于传统ADC的输入和基准电压源路径的缓冲放大器的选择。

图1.(a) 传统ADC的输入和基准电压源上的反冲电流,(b) 通过缓冲器将反冲电流与输入和基准电压源隔离

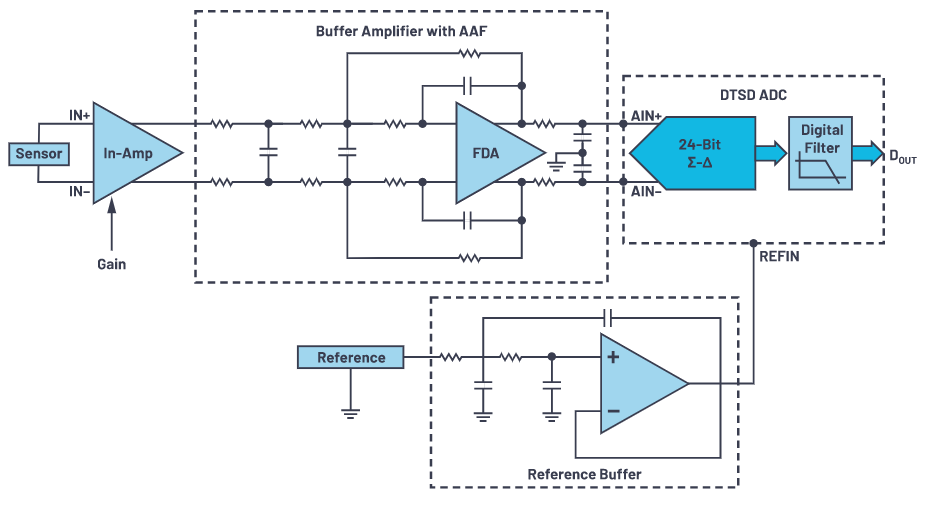

另一方面,输入端需要低通抗混叠滤波器来确保高频噪声和干扰信号大幅衰减,使得当它们因为目标频段的采样而折回时,性能不会降低。当前ADC信号链设计人员面临的挑战是要对相互对立的要求――混叠抑制和输出稳定――进行微调。DTSD ADC的采用驱动器和抗混叠滤波器的前端设计如图2所示。

输入路径由仪表放大器(in-amp)组成,仪表放大器将传感器与全差分放大器(FDA)接口,后者最终驱动ADC。仪表放大器将输入传感器环境与ADC电路隔离开来。例如,传感器的共模(CM)信号可能非常高(高达数十伏),但大多数FDA和ADC不支持这种高输入共模电压。一般的仪表放大器有能力支持宽输入共模电压,同时提供适合于FDA和ADC的输出共模电压。仪表放大器的另一个优点是其具有高输入阻抗。这意味着如果传感器不能直接驱动FDA的输入电阻,那么传感器可以通过仪表放大器与FDA接口。FDA本身需要具有高带宽和高压摆率,以使输出更快建立。FDA周围需要构建有源抗混叠滤波器(AAF),以便抑制干扰信号。

对输入或基准电压源的驱动器的要求相互冲突:一方面,快速建立需要高带宽,但另一方面,噪声和干扰信号的滤波需要低带宽。在基准电压源路径上,DTSD ADC信号链的前端设计如图2所示,基准电压源IC连接到一个缓冲器,后者驱动ADC的基准电压源负载。设计中还有一个噪声滤波器,用以截断基准电压源IC和缓冲器的超出某一频率的噪声。此滤波器的设计要求将在后文讨论。基准电压源缓冲器具有高带宽和高压摆率要求,以便更快地平息采样事件干扰。

本系列文章的第1部分已说明,使用精密CTSD ADC的新信号链可以比传统ADC的复杂信号链小68%。这种尺寸缩减可减少BOM,而且简单的设计有助于信号链设计人员加快产品上市。

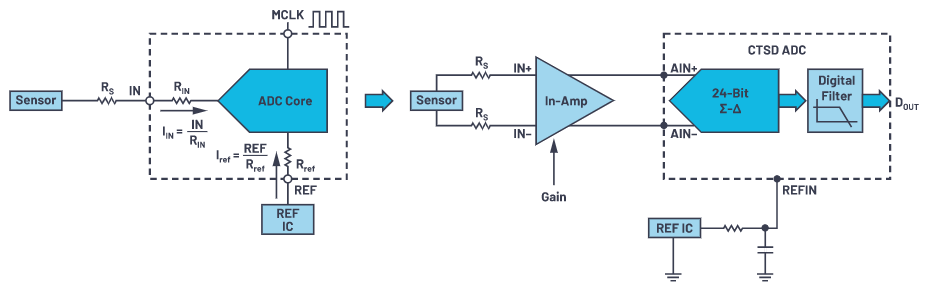

CTSD ADC的优势:正输入和基准电压源

第2部分向信号链设计人员解释了CTSD ADC架构,即采用非常规方法来反转闭环放大器。如第2部分所述,可以将CTSD ADC视为具有阻性输入和基准电压源负载的Sigma-Delta ADC。输入和基准电压源结构是简单的阻性负载,这意味着没有高带宽或高压摆率驱动要求。第3部分展示了CTSD的独特优势,其固有的混叠抑制能力可抗干扰。在传统信号链设计中,需要外部混叠抑制滤波器来衰减干扰信号,这是一个额外的挑战,但CTSD ADC不需要外部AAF。由于CTSD ADC的固有混叠抑制特性,调制器环路的信号转换函数等于衰减高频干扰的抗混叠滤波器的转换函数。由于阻性输入和固有AAF,输入网络得以简化,传感器可以直接连接到ADC。在传感器没有能力驱动这种阻性负载的情况下,可以使用仪表放大器来将传感器与ADC接口。类似地,在基准电压源方面,由于阻性负载,CTSD ADC信号链中不需要基准电压源缓冲器。图3b显示了使用仪表放大器的简化示意图。

图2.离散时间Sigma-Delta ADC的前端设计

图3.(a) CTSD架构提供阻性输入和基准电压源负载,(b) 直接仪表放大器和基准电压源驱动CTSD ADC

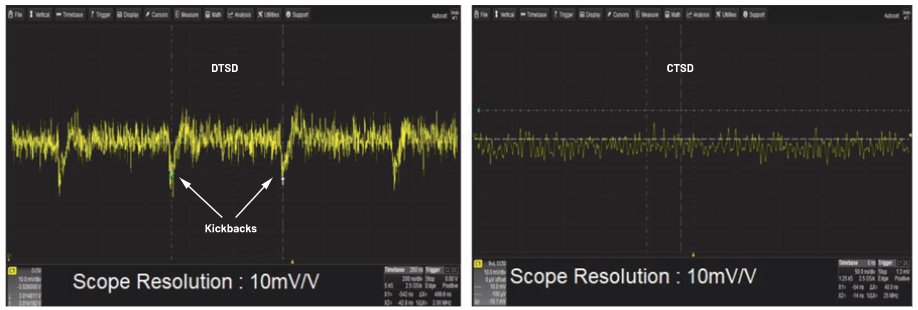

图4.(a) DTSD ADC的输入电流中的反冲,(b) CTSD ADC的连续输入电流曲线

图4显示了对CTSD ADC如何帮助简化输入前端设计的进一步支持。对于DTSD ADC,当输入采样开关改变状态时,可以明显看到反冲导致的输入电流的不连续性。对于CTSD ADC,可观察到输入电流是连续的,其保持了信号连续性。

简化输入驱动设计

我们已经证明,CTSD ADC的输入驱动是阻性的。本节将说明在规划ADC的输入驱动时,如何确定输入阻抗RIN的值。RIN是ADC额定噪声性能的函数。例如,AD4134是一款精密CTSD ADC,具有108 dB的动态范围和4 V基准电压源,输入阻抗为6 kΩ差分。这表明,当施加一个满量程8 V p-p差分输入信号时,峰值电流要求是1.3 mA p-p。如果传感器可以支持输入电流VIN/RIN,则它可以与ADC直接接口。需要一个简单放大器来驱动这种阻性负载的场景是:

1. 传感器没有所需驱动能力来提供VIN/RIN的峰值电流。

2. 信号链设计要求为传感器输出提供增益或衰减。

3. 将输入传感器环境与ADC电路隔离开来。

4. 传感器具有很大输出阻抗。

5. 传感器远离ADC,轨道布线可能给输入端增加相当大的电阻。

在场景4和5中,额外的外部电阻RS将存在电压降,该电压降表示ADC输入端有信号损失。这导致信号链的增益误差和误差随温度的漂移,因而引起性能下降。增益的温度漂移是由外部电阻和内阻的不同温度系数引起的。使用一个简单放大器来隔离额外的外部电阻,可以解决此问题。由于该放大器的驱动负载是阻性的,因此该放大器的选择标准是:

• 输入阻抗:为避免信号衰减或损失,传感器的阻抗应与放大器输入阻抗匹配。

• 输出阻抗:输出阻抗应当足以驱动ADC的阻性输入负载。

• 输出类型:作为一般信号链设计指导原则,建议使用差分信号策略以获得最佳信号链性能。差分输出类型放大器或单端转差分输出的设计技术最适合此任务。另外,为了实现最佳性能,最好将该差分信号的共模设置为VREF/2。

• 可编程增益:输入信号一般要放大或衰减,以将其映射到ADC的满量程范围。这是因为当使用ADC的满量程输入范围时,可以从ADC信号链获得最高性能。

基于应用,该放大器可以是仪表放大器或FDA,也可以是两个单端运算放大器的组合――形成一个差分输出放大器。没有高压摆率或高带宽的硬性要求,可根据应用需求从ADI公司广泛的放大器产品组合中选择一款来驱动此CTSD ADC。此外,放大器性能参数一般用阻性负载来指定,这使得选择更加简单。

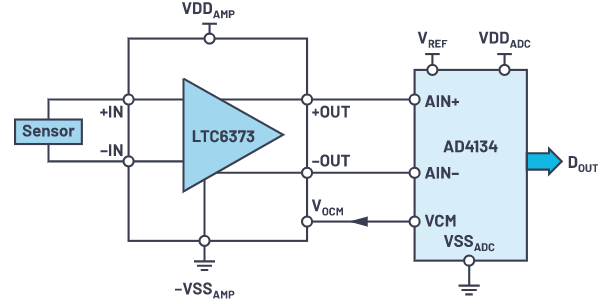

例如,对于AD4134,一个具有可编程增益选项和全差分输出的性能兼容的仪表放大器选择是 LTC6373。该仪表放大器为输入源提供高阻抗,可以轻松驱动差分6 kΩ阻抗,噪声和线性度性能与ADC相当。通过其广泛的输入共模支持和可编程增益选项,任何具有宽范围信号幅度的传感器或输入信号都可以与ADC接口。采用该直接仪表放大器驱动的输入前端设计的一个例子如图4所示。

图5.输入前端设计,CTSD ADC与仪表放大器直接接口

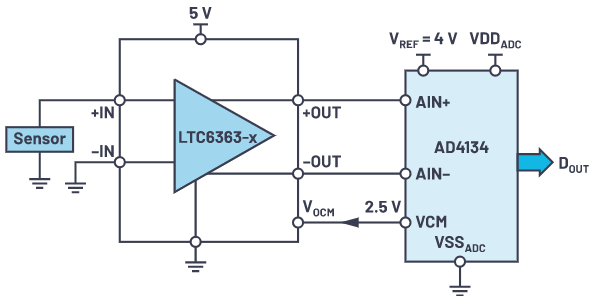

另一个例子是使用全差分驱动放大器(如 LTC6363-0.5/LTC6363-1/LTC6363-2,基于所需的增益或衰减)的简单低压前端设计,如图6所示。可以使用FDA的场景是当传感器有能力驱动FDA的阻性负载,但为单端类型或具有ADC不支持的共模,或者信号链需要小增益/衰减。

图6.输入前端设计,CTSD ADC与全差分放大器直接接口

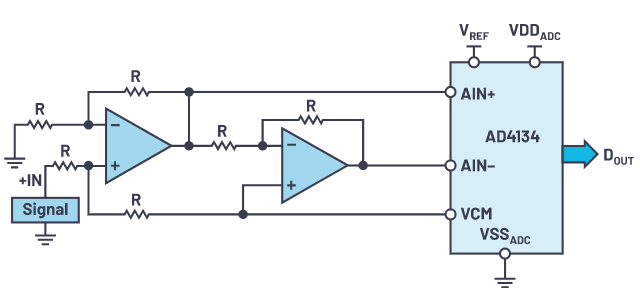

另一个例子是低BOM方案,使用两个单端运算放大器将单端输入转换为ADC的全差分信号,如图7所示。

图7.输入前端设计,CTSD ADC使用两个单端放大器

还有许多其他例子,像使用单端仪表放大器和单端运算放大器的组合来构建差分输出前端,以支持非常高的输入共模或低驱动强度单端型传感器。可以根据性能、面积和BOM要求选择任何这样的组合,以更好地适合应用。

与AD4134兼容的其他放大器有:

• 运算放大器 ADA4625-2、ADA4610-2、AD8605和ADA4075-2。

• 全差分放大器:ADA4940-2、LTC6363和ADA4945-1。

• 仪表放大器: AD8421。

ADI放大器选型指南 可用于选择最适合具体应用的放大器。例如,对于音频测试设备等高线性度应用,建议使用ADA4945-1。对于最重要考虑是超高输入阻抗的光电二极管应用,可以使用跨阻放大器(TIA),例如ADA4610-2。

CTSD ADC大大简化了输入前端,接下来看看基准电压源驱动方面的类似简化。

简化基准电压源设计

ADC输出是其输入和基准电压源的表示,如式1所示。

其中,VIN = 输入电压电平,VREFADC = ADC的基准电压,N = 位数,DOUT = ADC数字输出。

式1说明,为实现最佳ADC性能,干净完好的基准电压源十分重要。ADC有如下三个主要性能指标会受基准电压误差影响:

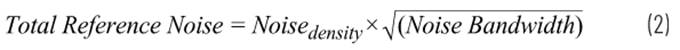

• 信噪比(SNR): SNR的主要噪声贡献源是输入路径、ADC本身和基准电压源。对于ADC输出端的目标总噪声,考虑到其他噪声源,基准电压源噪声的预算一般是独立ADC输出噪声的1/3或1/4。基准电压源或基准电压源缓冲器通常具有比ADC更高的噪声。在基准电压源或基准电压源缓冲器IC的数据手册中,可以看到频谱噪声密度或Noisedensity是技术规格之一。回顾噪声计算基础,基准电压源或基准电压源缓冲器输出端的总噪声由下式给出:

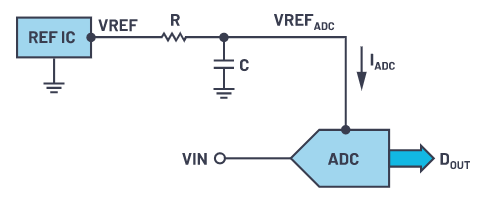

我们无法控制Noisedensity,因为对于所选的基准电压源或缓冲器,它是固定的。唯一可控参数是噪声带宽(NBW)。为了降低基准电压源噪声,我们需要降低基准电压源或基准电压源缓冲器的噪声带宽。这一般是通过将一阶低通RC滤波器连接到ADC来实现,如图8所示。对于一阶RC滤波器,NBW由下式给出:

• 流过滤波器电阻R的ADC基准电流IADC引起一个电压降,这会改变ADC的实际基准电压值。因此,建议选择较小的R值和较大的C值,以满足低基准电压源噪声的NBW要求。

• 增益误差:从式1可以看出,VREFADC决定了输出到输入转换函数的斜率,就像在y = mx之类的直线方程中一样。该斜率也被称为ADC的增益。因此,如果基准电压源发生变化,ADC的增益也会改变。

• 线性度:对于传统的DTSD ADC和SAR ADC,基准电流和伴随的反冲依赖于输入信号。因此,如果基准电压源在下一个采样时钟边沿之前没有完全建立,则基准电压源上的误差将与输入相关,并导致非线性。数学上,VREFADC可表示为

参考式1,基于ADC的输入,ADC输出DOUT将有各种高阶依赖性,这种依赖会造成谐波和积分非线性。因此,传统ADC硬性要求基准电压源缓冲器具有高压摆率和带宽,以使基准电压源输出在采样时间周期内稳定下来

如果仔细分析SNR和线性度,我们会看到基准电压源或基准电压源缓冲器具有相互冲突的要求要满足。低噪声要求低带宽,但快速建立要求高带宽。适当地平衡这两项要求是信号链设计人员长久以来的挑战。一些最新的DTSD ADC和SAR ADC将基准电压源缓冲器整合到片内,以简化信号链设计中的一步,但这些解决方案需要额外的功率,或者会在一定程度上影响性能。CTSD ADC不需要快速建立缓冲器,其阻性输入也不需要快速建立驱动器,因此能够避免性能问题。

CTSD ADC通过以下特性和设计改进解决了基准电压源驱动器的挑战:

• 基准电压源为阻性负载,在每个采样时钟边沿没有建立要求。因此,设计人员可以直接将基准电压源IC连接到ADC,而无需专用基准电压源缓冲器。

• 已获专利的设计技术使基准电流与输入无关,并迫使ADC的基准电流IADC基本保持恒定。当可能需要RC滤波器来降低基准电压源噪声时,这是有益的,如图8所示。结果是电阻上的压降恒定,没有输入相关项增加到VREFADC上。我们设计了一项措施,可以根据R的值和基准电压引脚上测得的电压来对系统级增益误差进行数字校正。因此,这个简单的基准电压源接口不会有增益或线性误差。

图8.阻性基准电压源负载支持基准电压源IC与无源滤波器直接连接

尽管已经采取措施来对R上压降引起的误差进行数字纠正,但有人可能会问,这是否会限制CTSD ADC的满量程范围,因为ADC的实际基准电压(VREFADC)会比施加的VREF要小。

例如,若将基准电压源IC的VREF调整并设置为4.096 V,ADC基准电流(IADC) = 6 mA,那么,对于R = 20Ω的滤波器电阻,ADC的实际基准电压(VREFADC)为3.967 V,如式5所示。在这种情况下,当在ADC输入端施加2×VREF = 8.192 V p-p(其大于2×VREFADC)的额定满量程差分输入时,是否有可能使ADC输出饱和?答案是"不会"。CTSD ADC设计为支持输入幅度超出ADC引脚REFIN的基准电压几mV。在我们的AD4134示例中,该扩展范围将电阻值限制为最大25Ω。然后选择用于噪声滤波器的C值,以满足所计算的噪声带宽。

简化基准电压源驱动设计

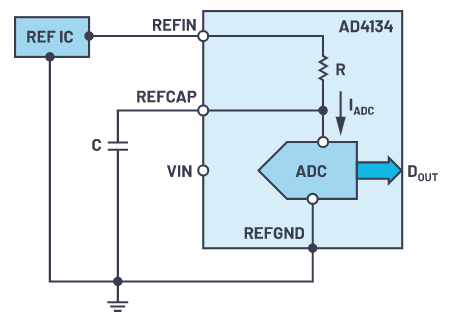

CTSD ADC简化了基准电压源驱动的设计,但当为滤波器选择正确的R,然后对电阻上的压降进行数字增益误差校正时,仍有其他因素需要考虑。数字增益误差校正(也称为校准)是许多ADC的常见特性,它让信号链设计人员可以在ADC的数字输出端自由补偿信号链中的误差。因此,它可能不需要增加设计步骤,而是重复使用相同的算法,这对于许多信号链很常见。在这种情况下,电阻的选择似乎不是什么特别的设计步骤,但有一点要注意:电压降的温度相关性。外部滤波器电阻与IADC随温度的漂移不同,进而导致VREFADC和ADC的增益随温度漂移。对于具有严格增益漂移要求的应用,一种原始解决方案是定期校准信号链。但是,借助CTSD技术可以实现更好、更创新的解决方案。由于ADC基准电压源负载电流保持恒定,而且与片内使用的阻性材料有关,因此可以提供片内20Ω滤波器电阻R,如图9所示。

图9.片内基准电压源噪声滤波器电阻简化CTSD ADC的基准电压源前端设计

在新的前端设计中,基准电压源IC连接在REFIN引脚上,滤波电容连接在REFCAP引脚上,形成基准电压源IC噪声的噪声滤波器。由于片内电阻R的阻值和IADC均是同一电阻材料的函数,因此REFCAP上没有温度漂移(VREFADC)。AD4134还使用已获专利的片内基准电压源校正算法对片内电阻上的电压降进行数字自校准。因此,基准电压源驱动设计得以简化,只需根据性能要求选择基准电压源IC和电容值。

ADR444是可用作CTSD ADC配套器件的低噪声基准电压源IC之一。关于电容值选择和内部/外部数字增益校准,AD4134的数据手册提供了进一步细节。

结论

CTSD ADCS消除了实现最佳精密性能并简化前端设计的许多障碍。在接下来的文章中,我们将介绍如何将CTSD ADC调制器内核的输出处理成最终数字输出格式,以供外部数字控制器使用,实现最佳处理。从本系列文章介绍的Sigma-Delta基础知识可知,调制器输出无法直接处理,因为它是以高得多的速率进行采样。需要将采样速率降低到应用所需的输出数据速率(ODR)。接下来,我们将介绍一种新颖的异步采样速率转换(ASRC)技术,它使信号链设计人员可以将最终ADC输出调整到所需的任何ODR,ODR只能是采样频率的几倍的古老限制不复存在。请继续关注这些有趣的见解!

参考电路

“驱动精密转换器:选择基准电压源和放大器。” ADI公司。

Mahaffey,Anna。“驱动SAR ADC(第1部分):模拟输入模型”。ADI公司。

Shah, Anshul。“为何基准电压噪声非常重要?” 模拟对话,第54卷第1期,2020年3月。

作者

Abhilasha Kawle

Abhilasha Kawle是ADI公司线性和精密技术部模拟设计经理,工作地点位于印度班加罗尔。她于2007年毕业于班加罗尔印度科学理工学院,获电子设计和技术硕士学位。

Roberto Maurino

Roberto Maurino是ADI公司位于英国纽伯里的精密ADC部门的设计工程师。2005年获伦敦帝国学院博士学位,1996年获意大利都灵理工大学和法国格勒诺布尔国立理工学院工程学位。

吃瓜群众路过点赞