Rambus将AI/ML训练应用程序的HBM2E性能提高到4.0 Gbps

2020年09月11日 16:20 发布者:eechina

Rambus Inc.宣布它的 HBM2E内存接口解决方案实现了创纪录的4 Gbps性能。该解决方案由完全集成的PHY和控制器组成,搭配业界最快的,来自SK hynix的3.6Gbps运行速度的HBM2E DRAM,该解决方案可以从单个HBM2E设备提供460 GB/s的带宽。此性能可以满足TB级的带宽需求,针对最苛刻的AI/ML训练和高性能的加速器计算(HPC)应用而生。

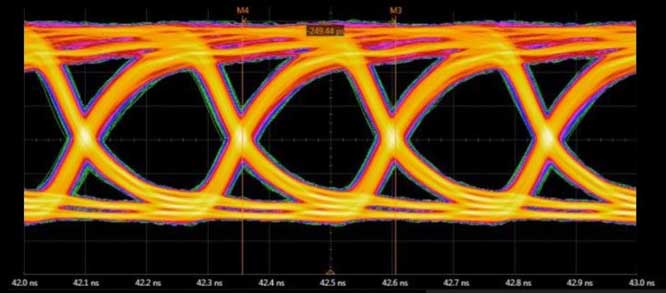

Rambus HBM2E 4Gbps 发送端眼图

“基于Rambus取得的此成就,AI和HPC系统的设计师们进行系统设计时就可以使用来自SK hynix 以3.6Gbps的速度运行世界上最快的HBM2E DRAM,” SK hynix 发言人,产品计划副总裁Uksong Kang说道。“今年7月,我们宣布全面量产HBM2E,可用于要求最高带宽的最新计算应用程序。”

完全集成并已可投产的Rambus HBM2E内存子系统以4Gbps的速度运行,无需要求PHY电压过载。Rambus与SK hynix和Alchip的合作,采用台积公司领先的N7工艺和CoWoS先进封装技术,实现了HBM2E 2.5D系统在硅中验证Rambus HBM2E PHY和内存控制器IP。Alchip与Rambus的工程团队共同设计,负责中介层和封装基板的设计。

台积公司设计基础设施管理部资深部长Suk Lee表示:“Rambus及其合作伙伴基于台积公司先进的制程工艺和封装技术所取得的进步,是我们与Rambus持续合作的又一重要成果。我们期待与Rambus继续合作,以实现AI/ML和HPC应用程序的最高性能。”

“透过本次合作,Alchip在7奈米和2.5D封装设计方面取得了显著的成功,”Alchip Technologies首席执行官Johnny Shen说。“我们为Rambus的突破性成就所做的贡献感到非常自豪。”

Rambus拥有30年的高速内存设计经验,并将其应用于最苛刻的计算应用。其著名的信号完整性专业知识是实现能够运行4 Gbps的HBM2E内存接口的关键。这为满足AI/ML训练中永不满足的带宽需求立下了一个新的标杆。

“随着硅运算速度高达4 Gbps,对设计师们而言,可验证未来HBM2E升级实现方向,并有信心为3.6 Gbps的设计提供充足的裕量空间。” Rambus IP core 总经理及资深总监 Matthew Jones说道:“参与每个客户项目过程,Rambus提供2.5D封装和中介层提供参考设计,以确保任务关键型AI/ML设计一步到位成功实现。”

Rambus HBM2E内存接口(PHY和控制器)的优点:

• 实现了业界最高的每引脚4 Gbps的速度,基于单个3.6 Gbps HBM2E DRAM 3D设备提供460 GB的系统带宽

• 完全集成和验证的HBM2E PHY和控制器降低了ASIC设计的复杂性,加快了上市时间

• 包括2.5D封装和中介层参考设计,作为IP授权的一部分

• 提供Rambus系统和SI/PI专家直接对接咨询的管道,帮助ASIC设计人员确保元器件和系统的最好的信号和电源完整性

• 具有特色LabStation™软件开发环境,有效隔离问题,协助客户快速系统点亮、进行特性测试和调试除错、

• 支持高性能应用,包括最先进的AI/ML训练和HPC系统

更多关于Rambus接口IP,PHYs和控制器的信息,请访问以下网页rambus.com/interface-ip