采样率为192kHz的24位AD转换器CS5361原理及应用

2010年10月25日 11:44 发布者:analog_tech

1 CS5361的主要特性 CS5361是CRYSTAL公司推出的114dB、192kHz数据输出率的24位Δ-Σ结构音频AD转换器,其主要特性如下:

●采用多位Δ-Σ结构;

●具有24位转换精度;

●114 dB动态范围;

●总谐波失真+噪声优于-105 dB;

●系统采样率高达192kHz;

●功耗小于150mW;

●内部带有高通滤波电路或直流失调电压标定电路;

●内带线性相移数字抗混滤波器;

●支持5V到2.5V逻辑电平;

●采用差动输入结构;

●具有溢出检测功能;

●采用24脚SOIC或TSSOP封装形式。

CS5361是供数字音频系统使用的完整的模数转换器,可完成采样、模数转换、抗混滤波等功能,并最终产生以串行模式输出的、对应于左右两个输入通道信号的24位采样数据,而且其最高数据输出率可高达192kHz。

CS5361芯片采用具有优良噪声抑制能力的差动输入结构,并采用5阶多位Δ-Σ调制器,同时带有数字滤波器和抽样器,从而避免了需要外部抗混滤波器的麻烦。

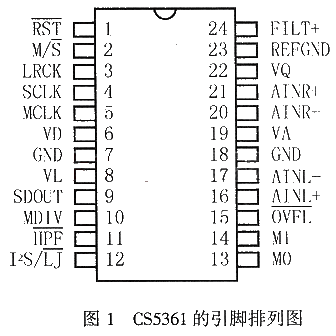

2 CS5361的引脚排列及功能

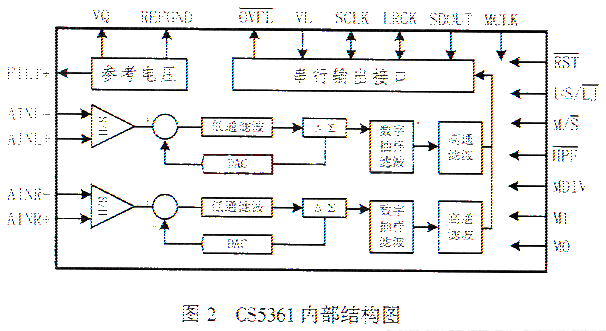

CS5361采用24脚SOIC或TSSOP封装,引脚排列图如图1所示。芯片内部结构图如图2所示。各引脚的功能如下:

RST:低功耗模式选择端,低电平有效;

M/ S:主、从模式选择引脚,该脚为低电平时,芯片为从工作模式;

LRCK:该端可用于决定当前串行数据属于左通道还是右通道;

SCLK:串行移位时钟端口;

MCLK:调制器和数字滤波器的时钟源;

VD:芯片数字电源;

GND:地参考,必须与模拟地相连;

VL:数字输入输出部分电源;

SDOUT:串行数据信号输出端;

MDIV:时钟分频端,该脚为高电平时,主时钟被2分频;

HPF:高通滤波器允许端,该脚为低电平时,高通滤波器工作;

I2S/LJ:数据输出格式选择端,该脚为高电平时,输出格式为I2S,否则为左对齐输出格式;

M0、M1:操作模式选择端;

OVFL:左右通道溢出指示脚;

AINL+,AINL-,AINR+,AINR-:分别为左右通道模拟信号的+、-输入端;

VA:+5V模拟电源输入端;

VQ:内部静态参考电压,使用时应连接滤波器;

REFGND:内部采样电路参考地;

FILT+:内部采样电路参考电压。

3 基本工作原理

CS5361转换器工作时,应根据工作的具体需要确定工作模式、操作模式、输出格式、高通滤波模式等工作参数,下面分别介绍这些参数的意义及设置方式。

3.1 操作模式及采样率范围选择

CS5361转换器的M1、M0引脚状态可用于决定芯片的操作模式,通过设置适当的操作模式,可使CS5361的输出采样率(FS)在2kHz到192kHz之间进行选择。每种操作模式对应的采样率范围如表1所列。

表1 工作模式与输出采样率范围对应表

M1

M0

操作模式

输出采样率范围(kHz)

0

0

单速模式

2~48

0

1

倍速模式

48~96

1

0

四速模式

96~192

1

1

保留

- - -

对于每种操作模式,芯片的性能可能略有差异,例如,工作在单速模式时,CS5361的数字滤波器的通带为0~0.47FS,阻带大于0.58FS,阻带衰减优于95dB,滤波器群延时为12/FS(S);工作在倍速模式时,CS5361的数字滤波器的通带为0~0.45FS,阻带大于0.68FS,阻带衰减优于92dB,滤波器群延时为9/FS(S);工作在四速模式时,CS5361的数字滤波器的通带为0~0.24FS,阻带大于0.78FS,阻带衰减优于97dB,滤波器群延时为5/FS(S),因此,应根据实际需要适当选择CS5361的操作模式。

3.2 系统时钟MCLK和MDIV状态

当CS5361的操作模式确定后,系统时钟和MDIV的状态将决定具体的输出采样率(FS)、左右通道时钟LRCK和串行移数时钟频率(SCLK)。

对于单速模式,其采样率范围为2~48kHz,因此,当MDIV为0时, MCLK的范围应为512kHz~12288kHz;而当MDIV为1时, MCLK的范围应为1024kHz~24576kHz;

对于倍速模式,采样率范围为48~96kHz,故在MDIV为0时, MCLK的范围应为6144kHz~12288kHz;为1时MCLK的范围应为12288kHz~24576kHz;

对于四速模式,由于其采样率范围为96~192kHz因此,当MDIV为0时,MCLK的范围应为6144 kHz~12288kHz;而当MDIV为1时, MCLK的范围则应为12288kHz~24576kHz。

3.3 主从模式设置

通过设置芯片的第2脚为高电平可使CS5361进入主模式,反之进入从模式。主从模式的区别在于进入主模式时,LRCK、SCLK为输出信号?而在从模式时,LRCK、SCLK为输入信号,并应保证LRCK、SCLK与MCLK同步,同时应使LRCK=FS、SCLK=64FS,否则将影响器件性能的发挥。设计主从模式的目的在于,多片ADC同步工作时,可以使其中的一片工作于主模式,其它工作于从模式,从模式ADC的LRCK、SCLK来自于主模式的ADC,这样可保证多片ADC的同步工作。

3.4 高通滤波器和直流偏移标定

由于CS5361转换器内部集成有数字高通滤波器。因此,可通过控制该芯片HPF引脚的状态来控制高通滤波器的工作状况,具体的方法是:当HPF为0时,内部高通滤波器将连续记录通道内的低频信号,并从抽样滤波器中滤除低于转折频率的低频信号,从而实现高通滤波功能。此时高通滤波器的转折频率为1Hz,高通滤波器的建立时间为105/FS(s);而当HPF为1时,高通滤波器记录的低频信号被冻结,并连续地从抽样滤波器中被扣除,从而实现直流偏移校正功能。与CS5361相连的模拟通道在工作时,可能会产生小的直流偏移,从而影响CS5361性能的发挥。因此,可以利用CS5361内部集成的数字高通滤波器将直流偏移校正掉,现将其工作过程说明如下:

(1) 开通高通滤波器,等待至少105/FS秒的时间以建立高通滤波功能;

(2) 高通滤波器建立后,禁止高通滤波器工作,冻结直流偏移值,此时芯片的输出即为去掉直流偏移后的数据。

应当说明的是:在此过程中,应始终保持CS5361处在正常工作状态。如果CS5361进入低功耗模式,那么高通滤波器中冻结的直流偏移值将被复位,此时若想实现直流偏移校正功能,则必须重复上述过程。

图3

3.5 数据输出格式控制

CS5361的数据输出格式有左对齐格式和I2S格式。通过控制I2S/LJ脚的状态可以选择数据的输出格式。

当I2S/LJ为0时,数据输出格式为左对齐格式;当I2S/LJ为1时,数据输出格式为I2S格式。两种格式的时序图如图3所示。

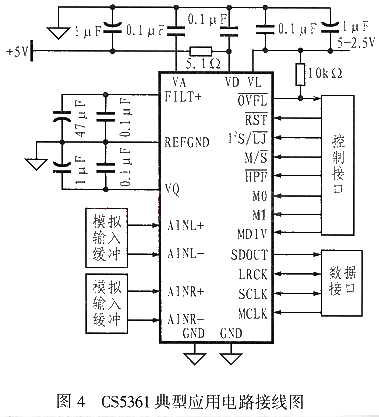

4 应用

同其它高精度AD转换器一样,CS5361在实际应用时,也应特别注意地线和电源线的布线。设计时必须为VA和VL提供干净的电源,当用VD给CS5361内部的数字滤波器供电时,可以通过一个电阻从VA上获取,也可以直接与系统的逻辑电源相连。而如果VD从VA上获取,则必须保证VD不再给其它数字电路供电。电源退耦电容必须尽可能靠近CS5361,而且应使小容量的电容更靠近ADC。所有信号,特别是时钟信号必须远离FILT+和VQ引脚,接在FILT+和VQ上的退耦电容必须放在与REFGND最近的位置。为了减小数字信号干扰,ADC的数字输出应该只驱动CMOS输入端。图4是CS5361的典型应用电路连接图。

由于ADC只以有限频率采样模拟信号,因此,高于一定频率的信号可能会引起假频信号。另外,由于ADC的输入阻抗有限,因此,在输入端还应加一定带宽的阻抗匹配电路,以改善ADC的性能。

由于ADC参考电压的源阻抗以及外部滤波电容的影响,系统上电后,必须经过一段时间,参考电压才能稳定,因此,必须等待一段时间后才能得到准确的测量结果。另外在实际使用CS5361时,还有以下几点需要注意:

(1)CS5361内部的数字滤波器为线性相移滤波器,因此应根据这一特点对不同频率信号的相位作出校正;

(2)CS5361在开始工作时,由于要等待滤波器稳定,因此在滤波器稳定前可输出2000个左右的无效数据,无效数据的具体个数与操作模式有关,此点应注意;

(3)CS5361从MCLK稳定到第一个数据出现,有一定的延时,延时大小与操作模式有关;

(4)CS5361转换器的四速模式和倍速模式时的信号带宽几乎完全一样,所不同的是四速模式时的输出采样率更高一些,滤波器的通频带也更宽一些,因此在满足采样率要求的前提下,应尽量采用低速操作模式,实际使用发现:CS5361在低速模式时的性能优于高速模式。

(5)利用CS5361的高通滤波器进行直流偏移校正时,它只是去除了做直流标定前通道所产生的直流偏移,而对于在采样进行中产生的偏移,此功能不起作用。

(6)CS5361的数据接口时序在左对齐格式和I2S格式时有很大的差别,这一点在使用时应引起足够的重视。

(7)CS5361通常以2的补码格式交替连续输出两个通道的24位采样数据,其信号满偏电压有效值为2V,这一点对格式变换十分有用。

(8)CS5361的两个通道数据虽然是交替分时输出,但同一组数据的采样时刻却是同步的,它们分别代表同一时刻的两个通道模拟信号的值。