多时钟域下同步器的设计与分析

2010年09月26日 14:16 发布者:eetech

在数字电路设计中,大部分设计都是同步时序设计,所有的触发器都是在同一个时钟节拍下进行翻转。这样就简化了整个设计,后端综合、布局布线的时序约束也不用非常严格。但是在设计与外部设备的接口部分时,大部分外部输入的信号与本地时钟是异步的。在SoC设计中,可能同时存在几个时钟域,信号的输出驱动和输入采样在不同的时钟节拍下进行,可能会出现一些不稳定的现象。本文分析了在跨时钟域信号传递时可能会遇见的问题,并介绍了几种处理异步时钟域接口的方法。 亚稳态

当触发器的建立时间和保持时间要求没有得到满足时,触发器就会进入一个界于逻辑1和逻辑0之间的第三种状态,即亚稳态。

理想的触发器是在时钟边沿到达的那个时刻采样数据。但是在实际电路中,时钟的跳变具有一定的斜率,电路采样、保存、传递数据也需要一定的时间。如果在数据还未稳定时进行采样,就可能会导致亚稳态的发生。

平均无故障时间MTBF(Mean time between failures)是指任意两次故障出现的间隔时间的期望值。一个系统亚稳态的MTBF是和系统频率、器件速度相关的指数函数:

或f都可以加大MTBF,即使两次故障出现的时间间隔加大。但在一般情况下,系统中的tr和f是固定的,故只能通过减小To、t或a来改善系统。降低输入信号的变化频率a可以满足建立时间和保持时间的要求。而To、t是器件的固有性质,只有用速度更快的器件才能减小它们。

是由触发器的电气特性决定的参数,可用于表征触发器翻转速度的快慢。增加tr,或者减小To、是异步输入每秒变化的次数。To和公式中的tr是有效的亚稳态最大分辨时间,是指触发器能够保持亚稳态输出,并不会引起故障的时间。f是触发器的时钟频率。

多时钟域下同步器的

设计与分析

当在某个时钟边沿采样一个变化的数据信号时,时钟边沿和数据变化这两个事件出现的先后顺序将决定结果。这两个事件出现先后的差异越小,判断哪个事件先到来所花的时间就越多。当两个事件到来太接近时,就会使判决所花的时间超过规定的分辨时间,从而导致故障发生。

异步信号传输的问题分析

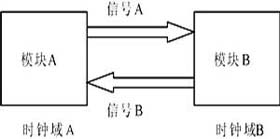

如果信号跨越不同的时钟域,就有可能会出现不满足建立时间和保持时间的情况。如图1所示,信号A经过组合逻辑传递到模块B中的触发器,若信号A到达时间与模块B的时钟边沿非常接近,模块B中的触发器就会工作在不确定的亚稳态。如果这个亚稳态持续了一个周期,就会影响到下一级的触发器,最终产生连锁反应,使整个芯片的功能发生混乱。

图1 多时钟域的信号传递

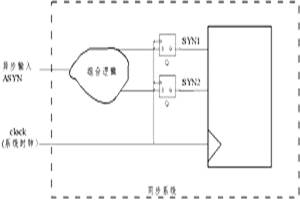

另外一种可能出现的现象如图2所示,由于在实际电路中存在延时,图中采样同一个异步信号的两个D触发器无法按理想状况接收到时钟信号和输入信号。因此,当异步输入在时钟边沿发生变化时,会出现在一段时间内,两个触发器的输出值SYN1和SYN2不一致的情况。这种不一致将会导致系统出现不正确的操作。

图2 异步信号传输通过不同路径

另外,图2中组合逻辑电路中的不同通路不可避免的具有不同的延时,因此,产生不一致结果的可能性就更大,这种情况在有异步信号输入的状态机里特别普遍。例如,某个VME总线接口芯片,用于完成VME总线时序到MC6000系列CPU时序的转换。CPU时钟是50MHz,VME总线系统的时钟是64MHz。VME总线是异步总线,存在很多跨越时域的握手信号,如果不使用同步器对与状态机的状态变量相关的信号进行同步化处理,就会出现故障。

同步器在多时钟域设计中的应用

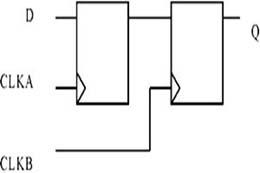

同步器的功能是采样异步输入信号,并使产生的输出信号满足同步系统的建立时间和保持时间的要求。简单的同步器一般采用D触发器来构成。图3中,D触发器的每一个时钟触发沿采样异步输入信号,并产生一个同步后的输出信号。要构建更好的同步器可以采用更快速的触发器,减小采样保持时间,使器件能够更快地采样到信号;或者增加MTBF方程中的tr值,等信号稳定后再采样,这可以通过延时采样来实现。

图3 同步器的构建和使用

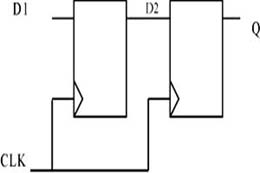

图4为最常用的一种同步器,与一级同步相比,两级同步能够更可靠地避免亚稳态的出现,而三级以上同步器的效果并不能提高多少。

图4 两级采样的同步器

同步器故障分析

如果同步器的建立时间和保持时间得不到满足,那么触发器同样会进入亚稳态。这个亚稳态通过不同的延时传到组合逻辑中,一部分电路把这个信号识别为逻辑1,一部分又将其识别为逻辑0,也会导致系统逻辑的混乱。

下面将比较一下一级同步器和两级采样同步器的差异。

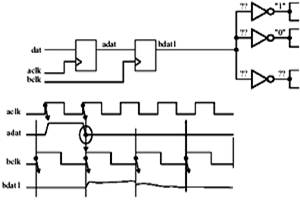

一级同步器如图5所示,aclk时钟域产生的信号adat的变化与bclk时钟域时钟的边沿采样太接近,未满足采样保持时间。同步器故障导致输出出现亚稳态,且在下一个时钟边沿到来之前,不会变成稳态。此输出传递到后面的组合逻辑中,导致系统混乱。

图5 一级采样的同步器故障

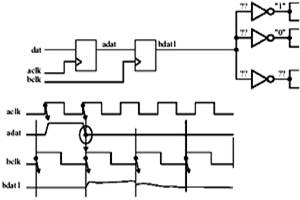

两级同步器如图6所示,当第一级触发器采样异步输入之后,允许输出出现的亚稳态可以长达一个周期,在这个周期内,亚稳态特性减弱。在第二个时钟沿到来时,第二级同步器采样,之后才把该信号传递到内部逻辑中去。第二级输出是稳定且已被同步了的。如果在第二级采样时第一级的输出仍然处于很强的亚稳态,将会导致第二级同步器也进入亚稳态,但这种故障出现的概率比较小。

图6 两级采样的同步器

两级同步器总体的故障概率是一级同步器故障概率的平方。例如,对74LS74系列器件来说, TO="0".4s,t=1.5ns,建立时间ts=20ns。设时钟频率为10MHz,则同步器分辨时间tr=80ns。若异步信号变化频率a=100kHz,则一级同步器的平均无故障时间为:

两级同步器的MTBF为2=1.296×1023s。在大部分的同步化设计中,两级同步器足以消除所有可能的亚稳态了。

结语

在异步设计时,同步化和亚稳态的问题是难以避免的。本文对该类问题做了较为详细的分析。文中介绍的同步器解决亚稳态和同步化的方案简单、可行性较高,能够满足绝大部分的逻辑设计。