һ���Կɱ��ʱ�Ӳ�����OmniClock���ṩ����������Ժͷḻ����

2016��07��07�� 10:23 �����ߣ�eechina

��ɭ���뵼�幩��ʱ���ǵ���ϵͳ�еĹؼ�Ԫ�أ������ܶ�����ϵͳ���ȶ���������������Ҫ�����á�OmniClock���ǰ�ɭ���뵼���Ƴ��Ŀɸ߶ȶ��Ƶ�һ���Կɱ��ʱ�Ӳ�����ϵ�У�������Թ����г����κοɱ��ʱ�������������ڿɴ����������ֻ���������������顢��Яʽ���Ӻ��������ȿ����Ӧ�ã�����С�ߴ硢���ġ��ͳɱ������ƵĴ���/�������ܵ����ơ�

OmniClockϵ�����Լ��������

OmniClockϵ��֧�ִ�8 kHz��200 MHz���������Ƶ�ʣ�����������ʱ�������LVCMOS/LVTTL�������߿�����ϳ�һ����������LVPECL��LVDS��HCSL / CML�����������Ա�������������/����������������ϵͳ�ɱ�����NB3H63143G����ͬʱ�ṩһ��50 MHz��125 MHz��48 MHzʱ�ӷֱ�CPU�ˡ��������CPU����ʵ�������ʱ��(BMC)�㷨����ͬʱ�ṩһ���ζ�50 MHz��һ�����156.25 MHz(LVPECL)ʱ�ӵ��������ĸ��ӿɱ��������(CPLD)����̫��������NB3V60113G�����ṩһ��25 MHz�� 0.125 %��ʱ�ӵ���̬Ӳ��(SSD)ģ���CPU�ˣ����ṩһ��27 MHz�� 0.5%��ʱ�ӵ�CMOS��������MCLK��ʱ�ӡ�

OE�����ʹ��

VDDO�������ѹ

��1. ��ɭ���뵼���ȫϵ��OmniClock������

1���ṩ�ɸ߶ȶ��Ƶ������

OmniClock�Ǿ��б������Clock Cruiser��ȫ���������������õIJ����������Ƶ�ʡ�������͡�����������������š��ڲ����ص��ݡ���Դ��ѹ�������ѹ���ο����롢�������š����(PLL)��·���Լ���Ƶ���õȵȣ���ϵͳ���Թ����У����������ü�ɿ����л��� �ܹ���ѵ����ܷ��������⣬�����Ա�ɴ洢��4�����������õ�һ���Կɱ���ڴ�(OTPM)�����������Ҫ������ʱ��ֱ���������ã���������ʱ��ͼ��Ϳ�档

2������ϵͳ�ɿ���

���þ���������ʱ���źţ����ܻ����һϵ�����⣬����·�岼��Ͳ��ߡ��¶Ⱥ͵�ѹ������ʱ�䳤����Ҫ����Ԫ���縺�ص��ݵȡ�ͨ����OmniClock������������弰��еʽԪ�����ɼ���ϵͳ���ֹ��ϣ�����ϵͳ�ɿ��ԡ�

3������ϵͳEMI (��Ÿ���) ��ֵ

��·����Ԫ��֮��IJ��߿��ܲ���DZ�ڵ�������EMI�� OmniClock�ڲ�PLL�ṩ��ȫ�ɱ�̵���ƵƵ�ʵ��ƣ�ͨ�����ֲ�ͬ����Ƶ���ÿɽ��ϵͳEMI��ֵ�������⡣��Ƶ���棬�����Ա��ѡ����Ƶ�����粻��Ƶ��������Ƶ��������Ƶ��ƫ��ٷֱ���������Ƶ��0.125%�����ġ�0.125% ����3%����������Ƶ��0.25%������-0.25%��-4%��Ƶ�ʵ��ƿ�ѡ30KHz ��130KHz֮�������ֵ����Ƶ���ƻ���PLL�������������PLL��·ģʽ�Ľ�����Ӱ�졣����Ҫ������ʱ��Ƶ�ʺ��������Ƶ���ü����Ȩ�⡣

4����ʡ�ռ䣬���ͳɱ�

����OmniClockʡȥ���弰�������������ص��ݣ���ʡռ��ռ䣬�Ӷ������ϵ��������ӶȺ�ϵͳ�ɱ�����֮���÷dz�С��QFN-16��DFN-8��װ������dz�С��������ÿռ伫С��Ӧ������

5������

������OmniClockϵ�е�һ���ؼ����ƣ����ӳ��ն˲�Ʒ���Яʽ�����豸�ĵ��ʹ��ʱ�䡣

OmniClock����USB��Ƶ����������ƴ���/����

USB��Ƶ�������ͨ����Ҫ����ο�ʱ������ͼ������ͼ��Э��������USB������ģ�������ڲ�ͬƵ�ʣ�����ʱ�Ӳ���������������ϵͳ��ƣ��ɸ��ƴ���/�������ṩ���õIJ�������ԣ��������Ծ������Ƶijɱ�����ϵͳ������

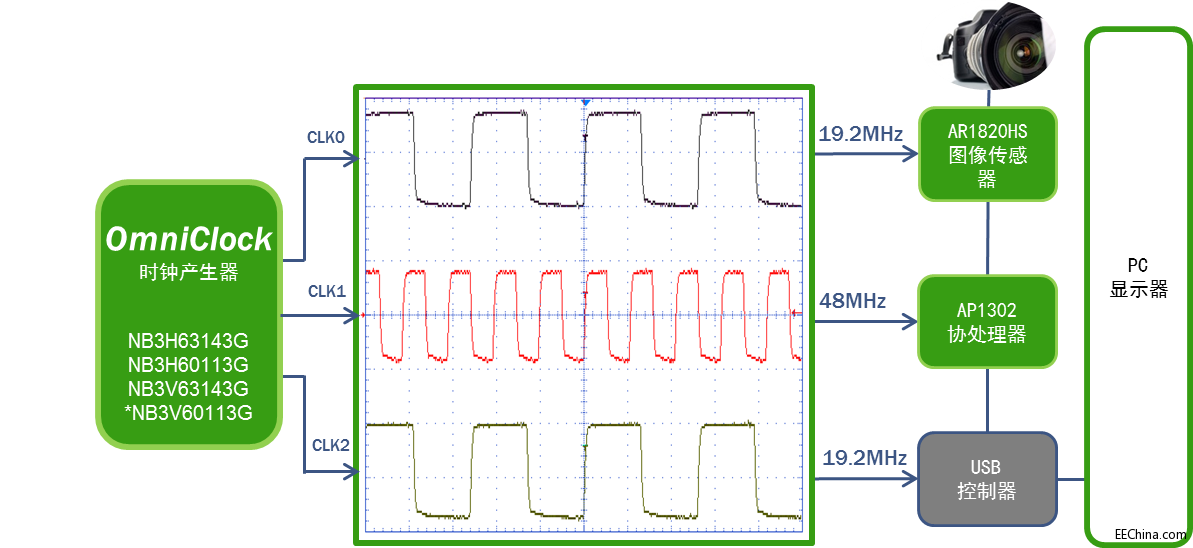

����OmniClock��������Ϊ֧��USB��Ƶ������������3��Ƶ�ʣ��ṩһ��19.2 MHzʱ�ӵ�AR1820HS 1800������ͼ������һ��48 MHzʱ�ӵ�AP1302ͼ��Э����������һ��19.2 MHzʱ�ӵ�һ��USB���������������;����������ɶ��Ƶ�Ƶ���������ϵ�����������ڶ�EMI���е�Ӧ�ö��������������ܡ�������Խ�һ��֧Ԯ������̣���ͨ�����������֤��̬����(OTP)����������С��װ��ƽ��͵�·�帴�ӶȺͳɱ���

ͼ1. OmniClock�ṩUSB��Ƶ������������3��Ƶ��ʱ��

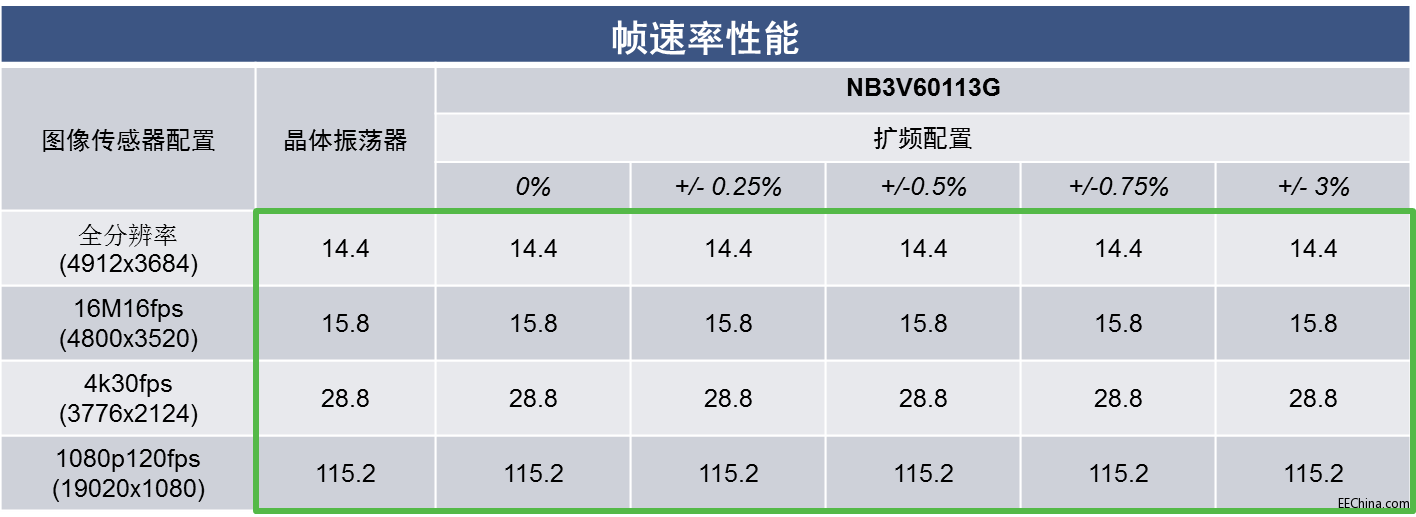

���������������ϵͳ����в��ýϳ��ı�ƽ���£�����ʱ�ӻ����EMIг����ֵ��OmniClock��Ƶ���ÿɽ��Ӧ�����е�EMI��ֵ���⣬�����ͳ������ܣ�������Ӳ������NB3V60113GΪ�������2��ʾ���������÷ֱ�Ϊȫ�ֱ��ʡ�16M16fps��4k30fps��1080p120fps��ͼ��������������֡���ʷֱ�Ϊ14.4 fps��15.8 fps��28.8 fps��115.2 fps��NB3V60113G����0%��+/- 3%�İٷֱȽ�����Ƶ��֡������Ȼ���ֲ��䡣

��2. OmniClock��Ƶ���ò����ͳ�������

���ע������

Ϊ�кõ�ʱ���ź��������Ծ�����С�������б�Ҫ�����źŷ��䡣����ϵ��ֻ����Դ�迹���ڸ����迹ʱΪ�㡣�����Ҫƥ���迹�Լ����źŷ��䡣��ͨ����������Ÿ�������һ����������������ȵؼ�С�迹���졣

Ϊʹ�������ܵ�ϵͳ��Դ������Ӱ�죬����װһ��0.1 uF��һ��2.2 uF��ȥ����ݵ���·�壬�Ҿ�������VDD���Ž�����VDD���ŵ���·�����ߺͽӵ�ͨ��Ӧ�������ܱ��Ͷ̡�����VDD���Ŷ�Ӧ����ȥ����ݡ�

����ź���LVDS���й�ģ�������ƺ͵������Ĺ������ƣ�֧�ֿ��ٿ����ٶȣ��ҹ��Ľ���������źű��ͣ��ȳ���LVDS�����������չ���ṩʱ���źŵ����LVDS�����������������Ե����ӵ����սڵ㡣

�ܽ�

OmniClockϵ��Ϊ��ǰ�г����κοɱ�̵�ʱ�������ṩ���Ĺ��ܺ�����ԣ���ϵ����������һϵ�о����ο�ʱ������Ƶ���Բ���һ·������(LVPECL, LVDS, HCSL, CML) ��һ·���ˣ������û������Ƶ�ʴ���·����LVCMOS�����֧�ִ�8 KHz��200 MHz���������Ƶ�ʣ���������/����������ʡռ���������������ϵͳ�ɱ�����Խ��ȫ���÷��������ϵͳ�����ƴ���/��������ǿϵͳ�ɿ��ԣ�ͬʱ����·����ƣ���ʹ�ͻ�����������ϵͳ���ĵ�Ҫ�Ⱦ������̽��ڣ��ɶ��Ƶ���Ƶ���û������ڶ�EMI���е�Ӧ�á�