基于谐波混频的微波低相噪锁相设计

2015年12月02日 13:36 发布者:designapp

0 引言众所周知锁相环的环路带宽以内的相位噪声主要由晶体振荡器经过倍频恶化后的相位噪声与鉴相器引入的相位噪声共同决定。对于环路带宽以外的相位噪声则主要由VCO的相位噪声和鉴相器引入的噪声基底恶化共同决定。也即是PLL对参考晶体噪声源呈现低通特性,而对VCO噪声呈现高通特性。因此通过常规的分频锁相方式,由于鉴相器鉴相频率较高以及噪声基底的恶化无法取得较好的相噪指标。

本振相位噪声水平很高的时候,射频输出的相位噪声与混频后中频信号的相位噪声基本上一致,这就提供了一种获得低相噪的解决方式,即通过谐波混频的方式降低鉴相器射频输入端的频率,并采用相噪水平很好的本振,基底噪声不会进一步恶化,这样系统输出的相位噪声由鉴相器的相位噪声决定。由于将鉴相器的射频反馈输入频率大大降低,使输出信号的相位噪声较之常规的分频式锁相环得以很大程度上的改善。

1 锁相源电路设计

1.1 电路指标

本次微波低相噪锁相设计的预期技术指标有:

(1)相位噪声:-110 dBc/Hz@10 kHz。

(2)工作频率:5.5 GHz。

(3)杂散水平:小于-60 dBc。

(4)输出功率:大于0 dBm。

1.2 电路设计

锁相环的基本组成是由VCO,鉴相器,低通滤波器,参考频率源等所组成。该设计所采用谐波混频与常规的分频式锁相系统不同,谐波混频锁相系统在反馈回路中并未采用一般的分频器而是采用谐波混频来对反馈的振荡信号进行处理在反馈给鉴相器的射频输入端口。这样做的目的在于使系统可以通过混频的方式取得相噪水平较好的中频信号反馈给鉴相器的射频反馈输入端实现锁相系统输出的低相噪的信号,这是分频式锁相系统难以达到的指标。其原理框图如图1所示。

该电路中鉴相器采用美国模拟器件公司的ADF4113,环路滤波器由RC积分滤波器构成,VCO的工作频率在5.5 GHz,这里采用Hittite公司的HMC431LP4。在设计中,预留了一个输入和一个输出端口,其中一个作为VCO的反馈信号送给谐波混频工作部分的输出端口,其输出端口的信号频率为5.5 GHz;另一个端口作为鉴相器反馈输入信号端口。5.5 GHz的射频信号在谐波混频工作部分中与本振为1.2 GHz的射频输入信号的四次谐波混频,最后输出700 MHz的中频信号反馈给鉴相器鉴相,从而得到控制电压控制VCO的输出信号频率,实现谐波混频锁相的功能。

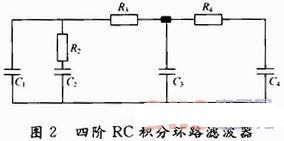

环路滤波器的输入端连接着ADF4113集成鉴相器,输出端连接着压控振荡器VCO。滤波器具有低通特性,可以起到低通滤波器的作用,但更重要的是它还对环路参数的调整起着决定性的作用,从而对环路性能产生重要影响。本设计采用四阶RC积分滤波器,如图2所示。

环路滤波器的输入端连接着ADF4113集成鉴相器,输出端连接着压控振荡器VCO。滤波器具有低通特性,可以起到低通滤波器的作用,但更重要的是它还对环路参数的调整起着决定性的作用,从而对环路性能产生重要影响。该设计采用四阶RC积分滤波器,如图3所示。

四阶RC积分滤波器的各部分作用如下:C1建立滤波;R2,C2建立锁相;R3,C3优化滤波;R4,C4进一步优化滤波。环路滤波器具体参数设计在此不再赘述。

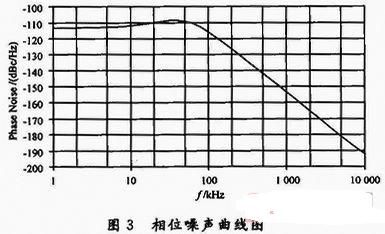

2 系统指标仿真与测试

采用AD公司提供的锁相环仿真软件ADI SimPLL,在输入频率为700 MHz,环路带宽为200 kHz时得到了环路相位噪声曲线和捕获时间曲线如图3,图4所示,可见相位噪声能够满足小于-110 dBc/Hz@10 kHz的要求,且环路能够在20μs内锁定。

最终本电路的测试图如图5,图6所示。由图5,图6可见相位噪声及杂散都能满足预期指标要求。

3 结语

该设计利用谐波混频实现了预期的全部主要指标,输出频率为5.5 GHz;输出功率为0.5 dBm;相位噪声达到-111.30 dBc/Hz@10 kHz;杂散抑制达到-67.33 dBc。该电路的杂散水平还可以通过合理走线得到的设置屏蔽盒等措施提高,并且混频工作部分只使用了高通滤波器,导致许多谐波信号也混杂在鉴相器的射频输入端而没有被滤除,如果使用5.5 GHz的带通滤波器效果会更好。