真正软件定义无线电的全新跨越

2015年11月30日 14:05 发布者:designapp

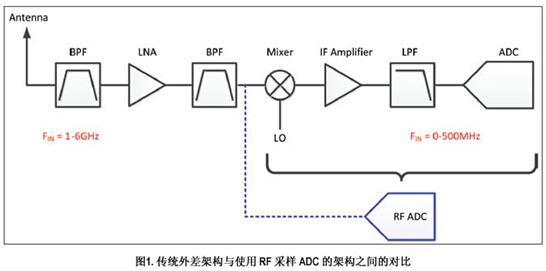

鉴于SDR的接收器仅仅由一个低噪声放大器 (LNA) 和一个滤波器和ADC组成,随着半导体行业在RF采样模数转换器 (ADC) 领域的进步,那些预见到真正软件定义无线电 (SDR) 的系统工程师们借此得以实现了之前的设想。例如:在RF波段范围处于700MHz到3.8GHz之间的蜂窝通信基础设施中,这一愿望就将很快成为现实。这是因为随着越来越多功能越来越强大的设备的涌现,能够满足用户对更小外形尺寸、更低系统功耗和更高密度的要求,从而让系统设计师的构想成为可能。目前的高性能接收器主要使用一种外差架构,在这种架构中,输入信号的RF范围在700MHz到数兆赫兹之间,随后下行转换为DC-500MHz之间的低中频 (IF)。例如在某些诸如军用雷达的应用中,当从10GHz(X波段)或者25至40GHz(Ka波段)范围内高很多的初级RF波段进行下行转换时,次级IF就在1至3GHz范围(S波段,L波段)。

RF采样ADC直接采集RF输入,并因此取代了图1中所示的整个下行转换级。由于不使用RF本地振荡器 (LO)、混音器和额外的增益与滤波级,从而节省了印刷电路板 (PCB) 面积,并可以实现更加紧凑的系统设计。ADC的兆赫兹采样时钟,在输入处于第二那奎斯特区间内或者更高区间内时,将已采样RF能量下行转换为较低的数字中间频率,从而成为高效LO。与外差架构中的混音器LO相类似,ADC时钟需要极佳的相位噪声来防止来自较大信号的能量混合进入小信号所处的同一频率,因为这样会降低接收器的灵敏度。

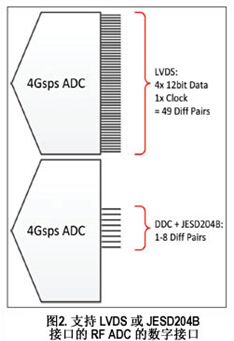

传统RF采样ADC需要极宽的数字接口来输出数据。由于低压差分信令 (LVDS) 通常情况下的速度最高只有大约1Gbps,所以一个12位,4Gsps ADC将会需要大约49个差分对(其中的48个用于数据,剩余的一个用于时钟)。这就要求足够大的封装尺寸,和在PCB上较大的走线面积。而例如ADC12J4000使用了一款10Gbps JESD204b接口,只用8个差分对即可传送同样的数据量―将所需的差分对数量减少了83%(图2)。对于窄带应用来说,片上数字抽取滤波器 (DDC) 可实现片上芯片滤波,以进一步减少数据流量和所需的信道数量。例如,一个带宽为100MHz的信号,只使用一条5Gbps的单信道即可以250Msps的速度进行传输(具有IQ输出的抽取因子32)。

RF采样ADC的信噪比 (SNR) 远远低于IF采样ADC,然而动态范围并没有变差。其原因是它们用过采样来弥补了其中的差距,并且通过将每赫兹水平的SNR标准化实现了差不多的SNR。

例如,信噪比为70dB SNR的14位,250Msps ADC的噪声频谱密度 (NSD) 为-151dBFS/Hz,而信噪比为55dB SNR的12位,4Gsps ADC的NSD为-148dBFS/Hz。它们之间的差异只有3dB。

RF采样ADC的优势

RF采样ADC有两个明显优势,一是将大量信号带宽数字化,二是直接在RF上捕捉信号,从而简化了信号链。

但它还有一个鲜少被提及的优势,即在所需信号波段远远小于采样率时,它能够使用快速采样率进行频率规划。选择一个至少比信号带宽快5至10倍的采样率可以使系统设计人员能够规划那些无法滤除的带内干扰源的负面影响,因此可实现更好的动态范围。

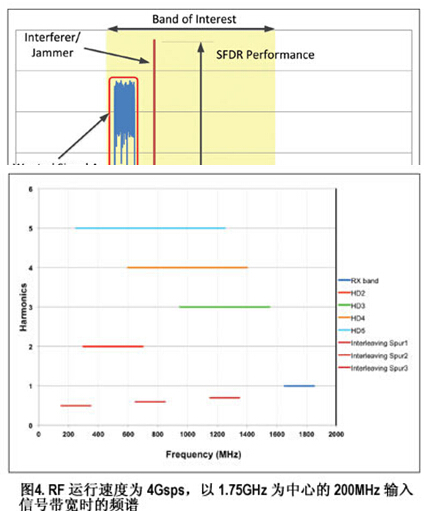

与外差接收器正好相类似的是,ADC的无杂散动态范围 (SFDR) 性能限制了对低输入信号的检测功能(图3)。所需带宽内的干扰源(或者是通信基础设施中的拦截器)是无法滤除的。这就要求信号链降低增益来避免ADC饱和。信号链中减少的增益会削弱把小信号(例如,“有用信号B”)提升到ADC噪底以上的能力,因而不能进行适当的检测。带内干扰源的谐波杂散还会落在有用信号的顶部,从而限制了接收器的灵敏度。这是军用雷达(用来侦测小型物体),软件定义无线电和蜂窝基站中的一个关键要素。

在过采样配置中使用RF采样ADC(诸如ADC12J4000)可以避免干扰源的限制谐波对小幅有用信号的阻断。例如,200MHz的所需带宽可在中央频率为1.75GHz的RF上,以4Gsps的采样率进行采样。前四个通常是高速ADC中最差的谐波(HD2,HD3,HD4和HD5),以及其他来自带内干扰源的交叉杂散就全都落在了波段之外(图4)。

ADC采样率的加快也放宽了对为驱动放大器所需的对抗混叠滤波器的要求。200MHz波段可以用500Msps ADC进行采样,但是将会需要非常精确的滤波器,这是因为下一个图像只隔了50MHz(假定波段在那奎斯特区域的中心)。相反地,采样率为4Gsps,以1.75GHz为中心的同一波段,就只需要和针对最近距离大约为300MHz的图像(混叠 = 2.15-2.35GHz,交叉图像 = 1150-1350MHz)同样的波段外滤波器衰减技术规格,对滤波器的要求就放宽了许多。

在成功使用频率规划后,SFDR性能只受到较高阶谐波(不是HD2-5中的任何一个)的限制。可以通过采用小信号抖动来进一步改进这些较高阶杂散。兆采样RF ADC的高采样率提供很多“未占用”频谱,可将波段受限抖动放置在其中,而又不会影响到任何有用信号(图5)。

抖动是软件定义无线电中的常用技术,并且可将杂散底噪改进5至10dB。

总结

目前诸如ADC12J4000的RF采样ADC可以大大提高超宽波段接收器的使用和性能。其高输入带宽在RF上直接实现了信号的数字化,与此同时,快速采样率又降低了滤波器要求,并实现了带内干扰器谐波周围的频率规划。通过添加片上数字滤波器来大大降低数字接口数据流量,从而使ADC12J4000成为小型、低功耗、下一代数字无线电的完美选择 。

作者:Tommy Neu,德州仪器 (TI)系统工程师