FPGA系统设计的仿真验证之: ModelSim的仿真流程

2015年11月24日 09:26 发布者:designapp

7.3 ModelSim的仿真流程7.3.1 ModelSim的安装

ModelSim的最新版本可以从互连网上免费得到,需要购买的只是License文件。ModelSim的下载地址为http://www.model.com/。打开网站页面后可以点击Download,用户填写完一张表格以后可以得到一个小时的下载时间。

获得License的方法有很多种。

首先可以在线申请License文件,选取“开始→程序→ModelSim SE 5.8c→Submit License Request”,会打开一个网页,填写信息以后点击Submit就可以在线申请License了。

另外也可以点击“开始→程序→Modelsim SE 5.8c→License Request Instructions”会打开一个文本文档,按要求填写好后发到指定邮箱即可。

在得到License以后点击“开始→程序→Modelsim SE 5.8c→License Wizard”,在弹出的对话框里面指定License文件即可。

7.3.2 使用ModelSim进行功能仿真

使用ModelSim对设计的HDL程序进行仿真分为功能仿真和时序仿真两种。本节将以一个具体的实例讲解如何使用ModelSim对HDL工程进行功能仿真。时序仿真的具体内容将在7.4节具体介绍。

这里我们使用的例子是一个分频电路的设计。所谓分频电路是将较高频率的时钟分频,得到较低频率的时钟。分频电路的使用较为广泛。

例如,我们要编写一个显示时间的电路就需要一个分频器,将晶振的频率分频得到1Hz的时钟信号。分频有几种方法。对于较为规则的分频,如2分频、4分频、8分频等,可以调用Quartus或者ISE本身的库函数来实现。

对于较不规则的分频,我们也有两种方法:一种是利用计数器的某一位作为分频输出,一种是计数器计数到某一数值时,分频时钟信号翻转来实现分频。两种方法的可以从其仿真结果得到。

之所以选择这个例子,是因为这里例子有实用价值并且设计本身简单,仿真也较为简单。

(1)新建工程。

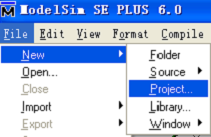

如图7.6所示,在ModelSim软件中选择“File”菜单的“New”选项,选择“Project”选项。打开如图7.7所示的新建工程对话框。

图7.6 新建工程 图7.7 新建工程对话框

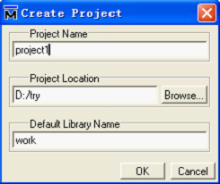

在该对话框中填写工程名称,路径和库。单击“OK”按钮,弹出如图7.8所示的添加工程项目对话框。

选择向工程添加的项目类型,然后单击“Close”按钮完成工程的建立。在此例中选择“Add Exiting File”项目。

(2)加入文件。

在新建工程时,也可以不选择添加的项目种类、而是在project栏里面单击右键,在弹出的菜单里面选择“Add to Project → Existing File”,如图7.9所示。

图7.8 添加工程项目 图7.9 添加存在的工程项目

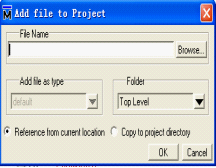

在弹出的添加文件对话框中,选择要添加的文件,如图7.10所示。

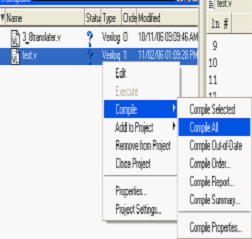

(3)编译文件。

在文件上面单击右键,选择“compile”选项下的“compile all”,如图7.11所示。

图7.10 添加文件对话框 图7.11 编译文件

当文件窗口中的“Status”栏的问号图标变成一个勾的图标时,说明编译成功。

(4)仿真文件。

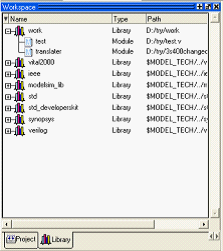

在Workspace的“Library”选项卡中,在work子目录里面双击test文件图标,就会自动完成仿真,如图7.12所示。

(5)查看波形。

编译成功以后,Workplace的“sim”选项卡将变成如图7.13所示的样子。

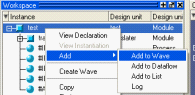

右键单击test,选择“Add”选项下面的“Add to Wave”选项,为波形窗口添加信号,如图7.14所示。

图7.12 选择需要仿真的文件 图7.13 编译成功后的test实例

图7.14 为波形窗口添加信号

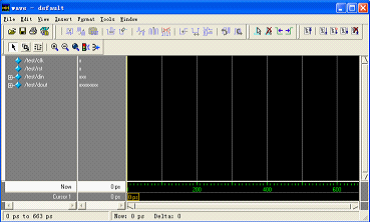

此时即可在新弹出的波形窗口中看到已添加的信号,如图7.15所示。

图7.15 波形窗口

单击工具栏中的

图标就能看见仿真结果了,如图7.16所示。

图7.16 仿真结果