认知无线电的频谱检测的FPGA实现

2015年11月09日 14:39 发布者:designapp

项目背景项目名称:认知无线电的频谱检测

项目背景:随着无线通信需求的不断增长,可用的频谱资源越来越少,呈现日趋紧张的状况;另一方面,人们发现全球授权频段尤其是信号传播特性较好的低频段的频谱利用率极低。认知无线电技术为解决频谱利用率低的问题提供了行之有效的方法。由于认知无线电在使用空闲频段进行通信的同时不断地检测授权用户的出现,一旦检测到授权用户要使用该频段,认知无线电用户便自动退出并转移到其他空闲频段继续通信,确保在不干扰授权用户的情况下,与他们进行频谱共享。这样一来,在没有增加新频段的情况下提升了用户量,且保证授权用户和认知用户通信的可靠性,大大提高了频谱的使用效率。

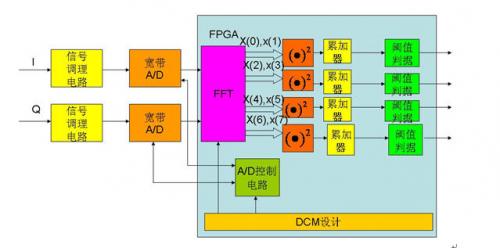

项目内容:本次课题主要研究认知无线电频谱检测的FPGA实现。目前最为常用的认知无线电频谱检测方法是能量检测。我们将一路电视信号下变频至基带信号再进入电路调理模块对信号进行50欧匹配,并对信号进行放大,然后用宽带A/D对信号进行采样,将采样后的数字信号做8点FFT运算,再通入能量和累加电路,最后通过能量阈值判决电路,判断频带的利用情况,从而找到频谱空穴,为认知无线电的功能实现打下基础。

项目难点:(1)高效低成本的FFT模块的设计与实现。

(2)累加器和阈值判决电路模块的设计与实现。

项目的开发意义:认知无线电的显著特征是具有认知能力,认知功能包括频谱感知,频谱分析和频谱判决。频谱感知用于频谱空穴检测,是认知无线电系统实现的前提之一。

硬件开发平台:Spartan 3E Board

频谱感知的背景知识

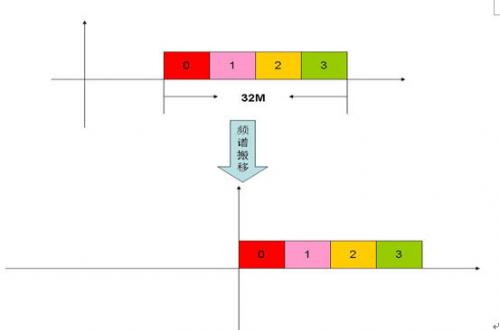

本次设计以四通道的电视信号为例进行实现,在我国一路电视信号的传输需要8M的带宽,那么传输四路电视信号需要32M的带宽才能实现。

我们将该四路电视信号进行复信号处理和频谱搬移,使其生成I,Q两路正交信号,其AD频率采样为32MHZ,为了检测各个通道的频谱利用情况,我们对复信号做FFT运算,其中x(0),x(1)包含在通道0当中,x(2),x(3)包含在通道1当中,x(4),x(5)包含在通道2当中,x(6),x(7)包含在通道3当中,然后我们分别对其做能量求和并进行实时监测,确定一阈值η,阈值判决电路对收到的信号跟阈值相比较,如果检测到信号大于η,那么认为授权用户正在使用该频段;反之,则授权用户没有使用该频段。

如图所示为频谱搬移的过程:

初步拟定硬件方案

(1)整体方案框图

本次设计使用8点的FFT设计,因此我们需要3级基2点的FFT运算,共有4个旋转因子需要存储,依据项目难点我们主要对FFT模块的设计进行逐层细化:

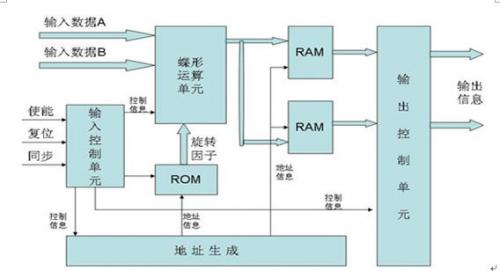

(2)一级FFT的系统框图实现

该框图为一级FFT的系统框图,输入数据A对应I信号的输入,输入数据B对应Q信号的输入,然后对其做基2点的FFT运算。

(3)ROM的设计

本次设计为8点FFT运算,就需要4个旋转因子,旋转因子的实部和虚部都采用八位二进制数来表示,因此使用一个宽度为16,深度为4的ROM存储器存储旋转因子。

(4)蝶形运算单元的FPGA实现

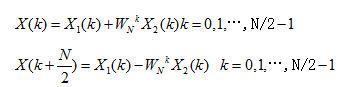

依据蝶形运算公式:

我们得到蝶形运算单元框图为:

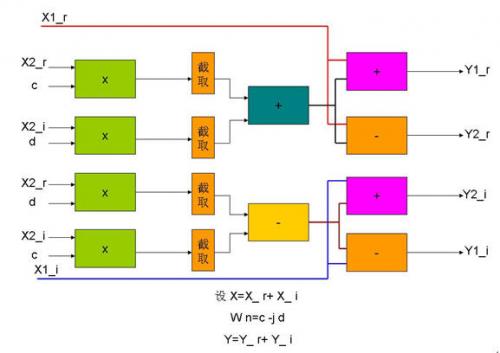

(5)乒乓结构的RAM示意图

我们在FFT模块中开辟两个RAM数据存储区,以此组成典型的乒乓操作模式;在FFT第一级运算中,数据从RAM1经蝶形运算单元计算存入RAM2,在第二次中则正好相反,以此类推…….,下图给出了乒乓结构的RAM示意图。

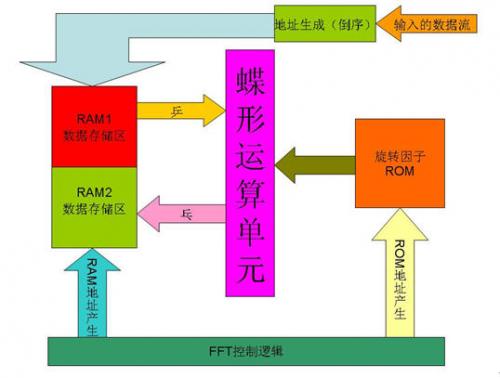

(6)能量求和模块

最终输出信号为:y=x(n)*x(n)+x(n+1)*x(n+1);

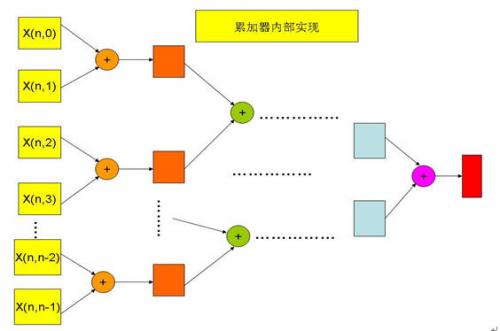

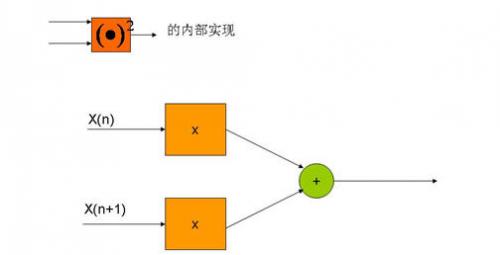

(7)累加电路模块

我们将能量计算模块计算出的能量值通入一个长度为n的FIFO结构,每当FIFO结构中有一个数据量发生变化时,累加器都要进行计算更新,这样就做到了实时监测该通道的频谱占用情况。在累加器当中,为了计算速度足够的快,可以满足实时性要求,我们往往设计为流水线结构。如下图所示:以流水线结构实现的累加器