TI C2000ϵ��TMS320F2837xD������Ӳ��������˵���飨�£�

2024��07��09�� 13:00 �����ߣ�Tronlong--

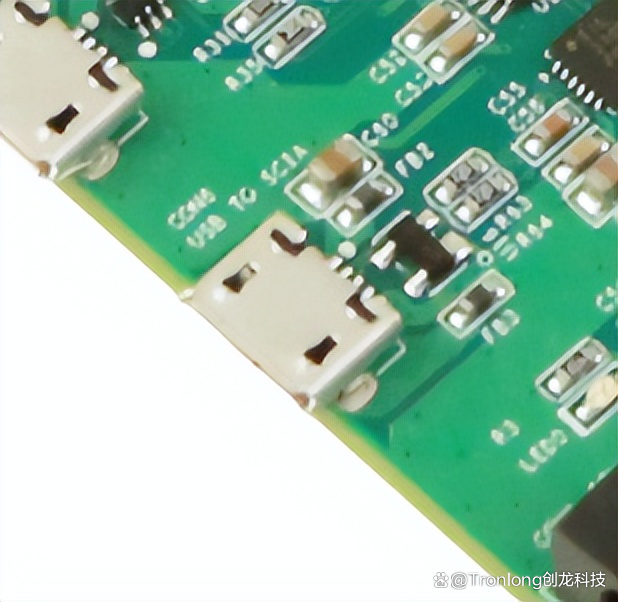

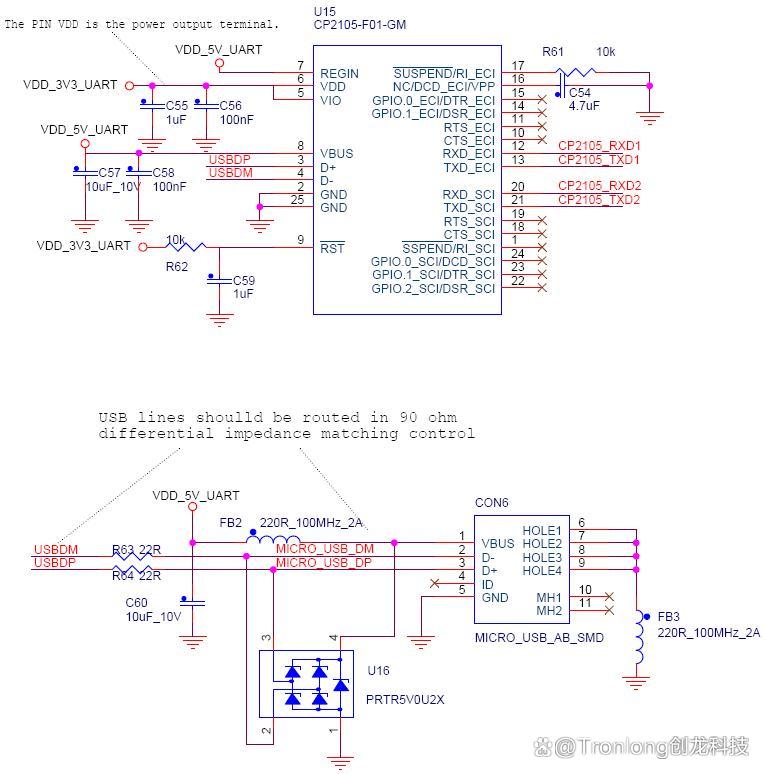

����USB TO SCIA����CON6(USB TO SCIA)ΪDSP��FPGA����һ���Դ��ڣ���ͬһ��Micro USB�ӿ�������

�����װ�ͨ��CP2105оƬ��DSP�˵�SCIRXDA��SCITXDA�ź�ת��Micro USB�ӿڣ���ΪDSP��ϵͳ���Դ���ʹ�á�ͨ��ͬһ��CP2105оƬ��FPGA��IOת��Micro USB�ӿڣ���ΪFPGA�˵��Դ���ʹ�á�

ͼ 30

ͼ 31

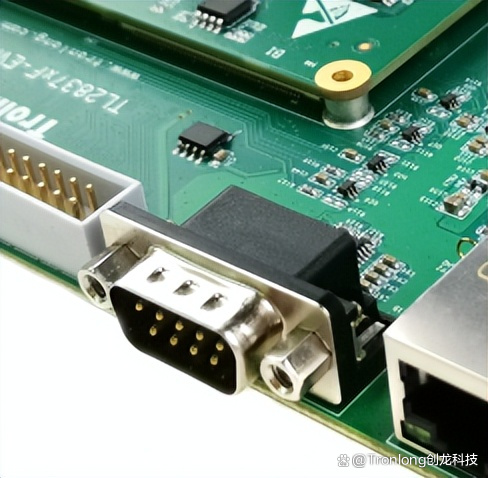

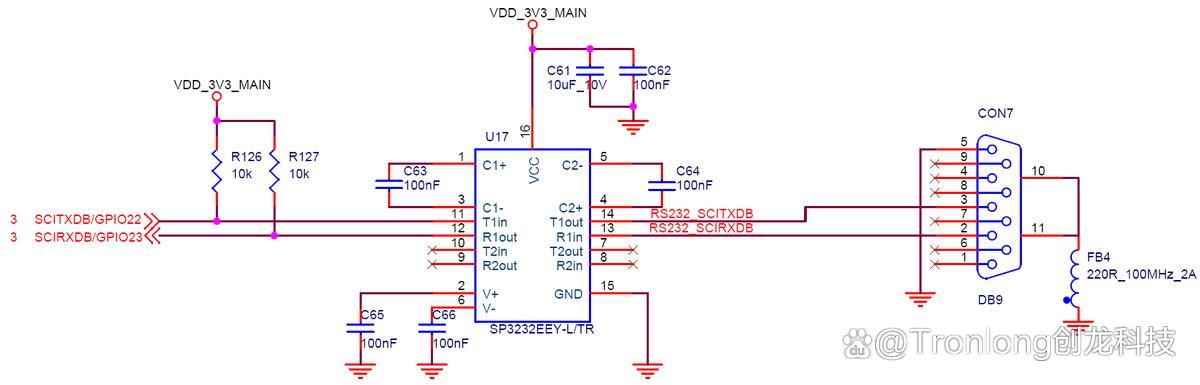

RS232 SCIB����

CON7ΪDSP��RS232�ӿڣ������װ�ͨ��SP3232EEY���ڵ�ƽת��оƬ��DSP�˵�SCIRXDB��SCITXDB�ź�ת��ΪRS232���ڣ��ӿ�ʹ��9��DB9�ӿڡ�

ͼ 32

ͼ 33

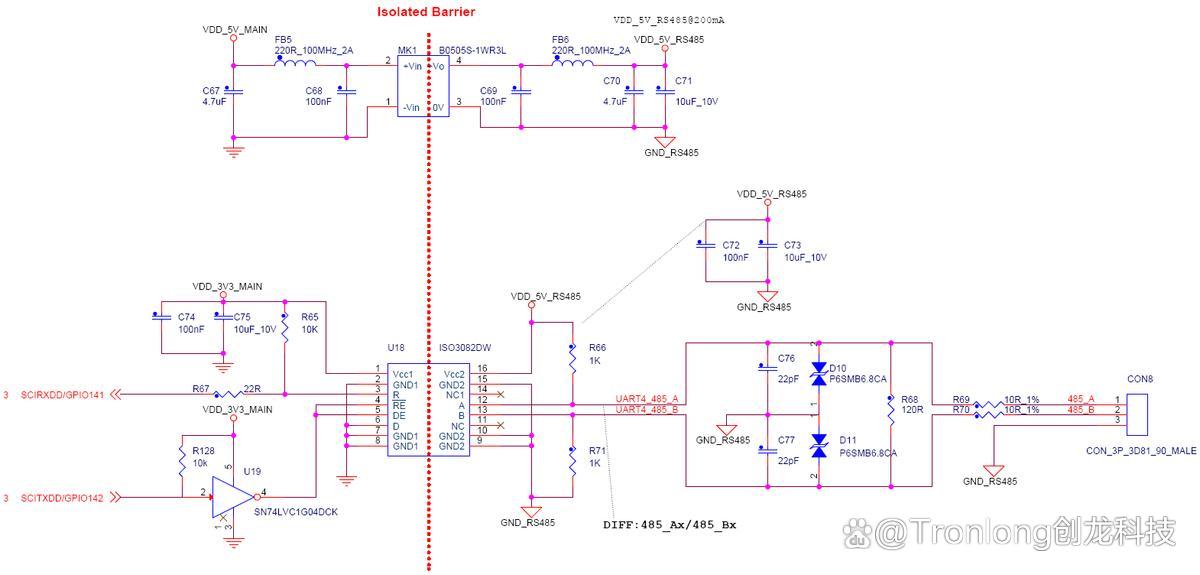

RS485 SCID����CON8ΪDSP��RS485�ӿڣ������װ�ͨ�������շ���ISO3082DW����DSP�˵�SCIRXDD��SCITXDD�ź�ת��ΪRS485���ڣ��ӿ�ʹ��3pin 3.81mm��ɫ���ӷ�ʽ��

ͼ 34

ͼ 35

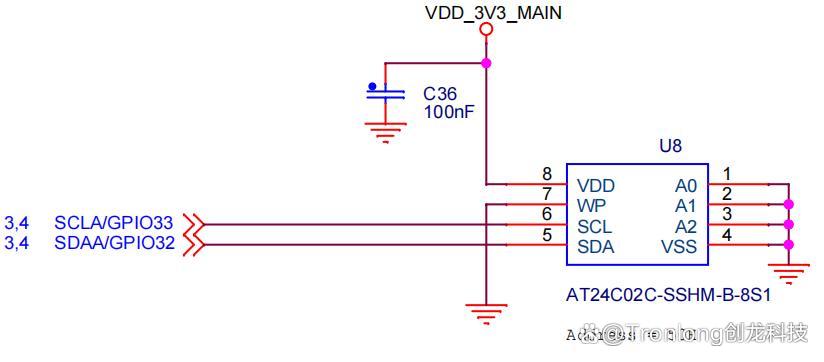

EEPROM

U8Ϊ����EEPROMоƬ������Ϊ2Kbit��������I2C���ߣ�I2C�豸��ַΪ0x50��

ͼ 36

ͼ 37

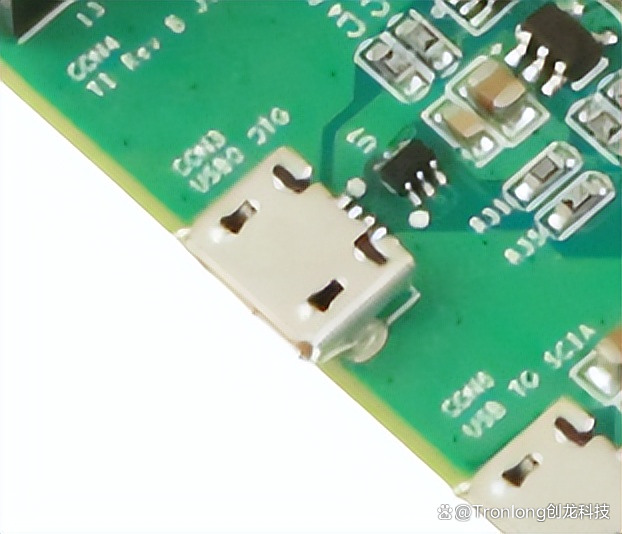

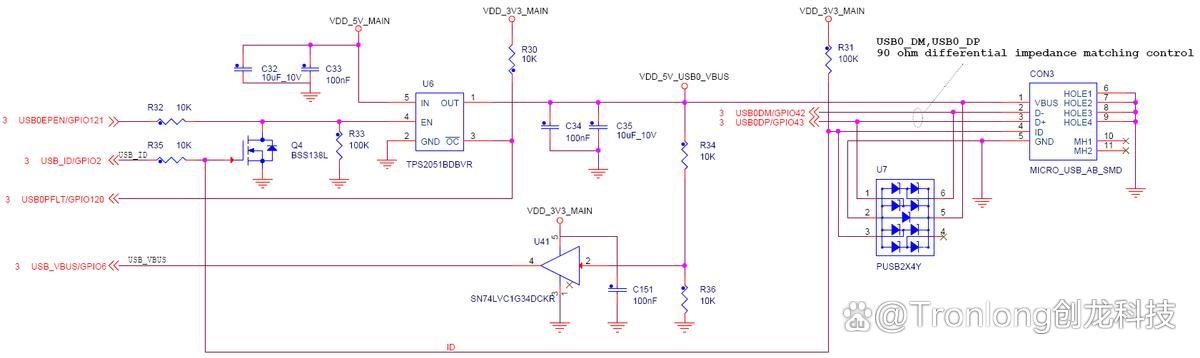

USB�ӿ�

CON3ΪUSB 2.0 OTG�ӿڣ�ֱ����USB0����(USB 2.0)������

ͼ 38

ͼ 39

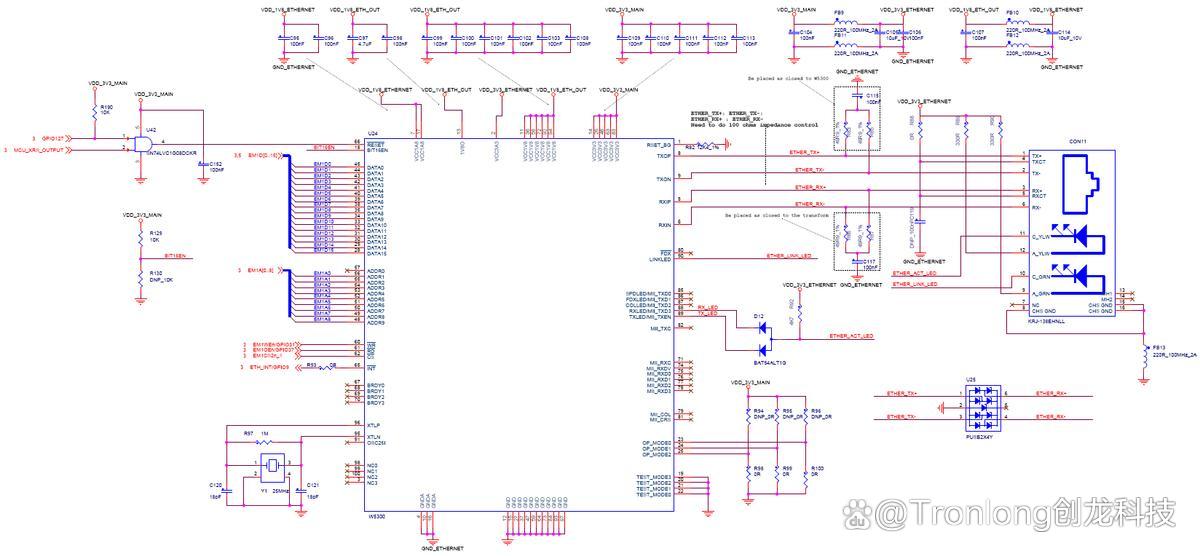

Ethernet�ӿ�

CON11(10/100 ETH)ΪDSP�˰������ڡ�TMS320F2837xDͨ��EMIF1��������W5300�������ڲ�����MAC��PHY������RJ45�����������������ڣ�RJ45�����������ø����ѹ����

ͼ 40

ͼ 41

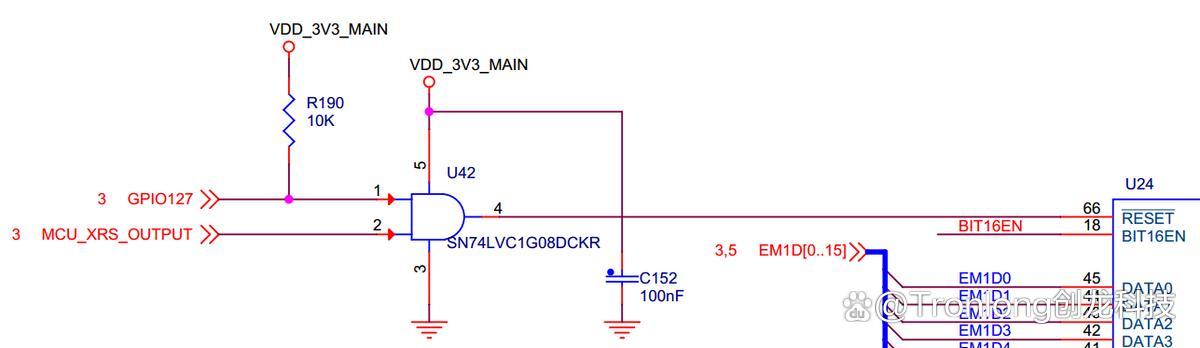

���ע�����

XTLP��XTLN���Ž���25MHz��Դ����Ϊ���ھ�������XTLP��XTLN֮������Ӳ���1M�����衣�Ƽ�����DSP��XRS + GPIO���Ƶ�·��������W5300����RESET���Ž��и�λ���ơ�

ͼ 42

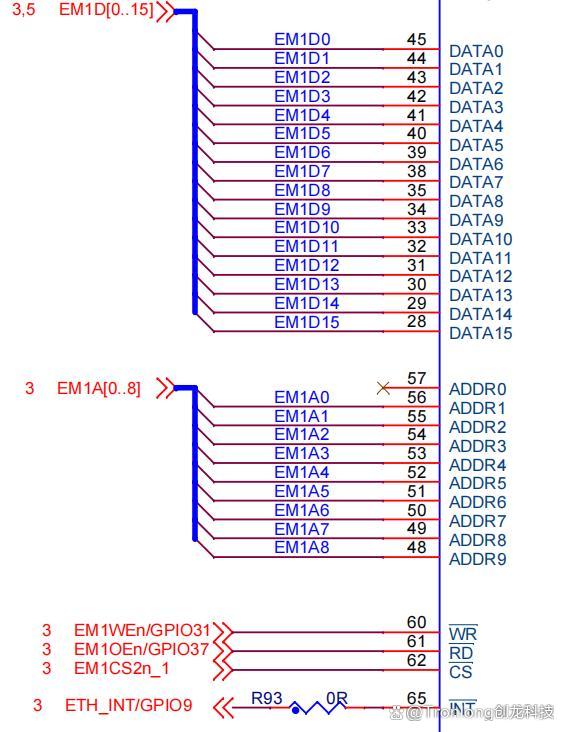

W5300����ʹ��DSP�˵�EMIF1�źţ�����Ƭѡ�ź�EM1CS2n_1��дʹ���ź�EM1WEn/GPIO31����ʹ���ź�EM1OEn/GPIO37����ַ����EM1A��16λ��������EM1D��W5300���ж�����ܽ�����DSP��ETH_INT/GPIO9����GPIO����Ϊ�ⲿ�ж����룬ͨ��EMIF1������W5300������������ͨ�š�

ͼ 43

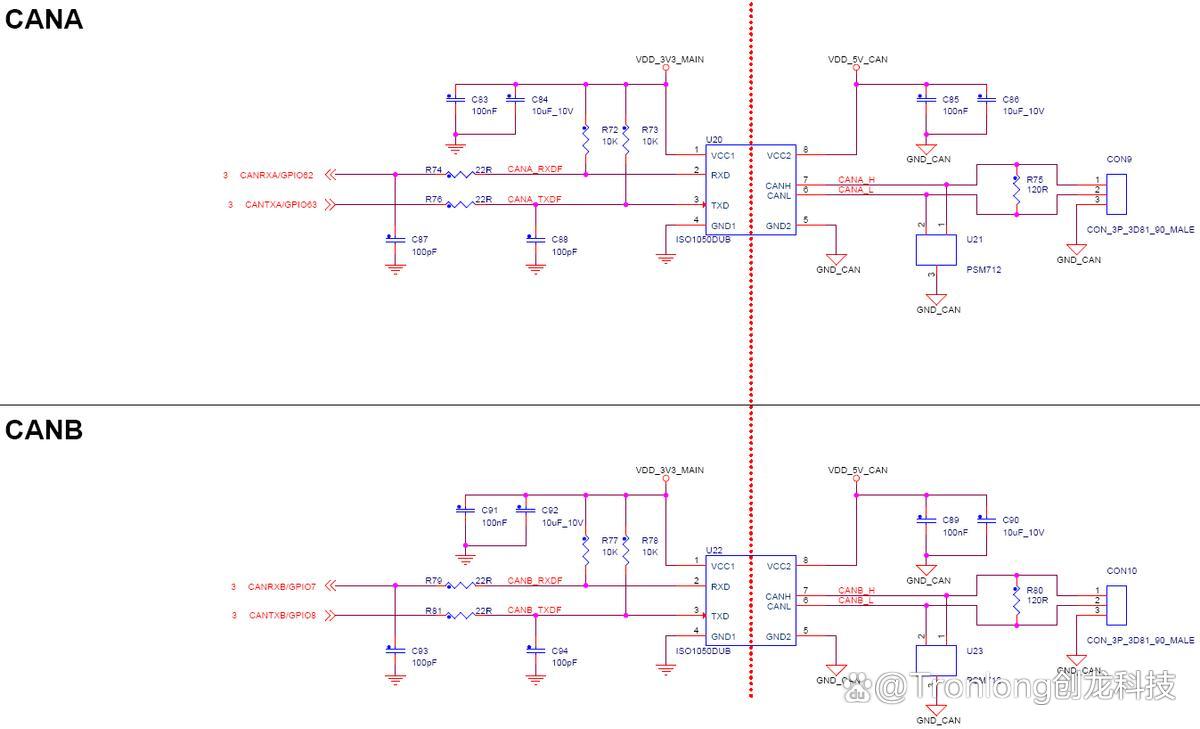

CAN�ӿ�

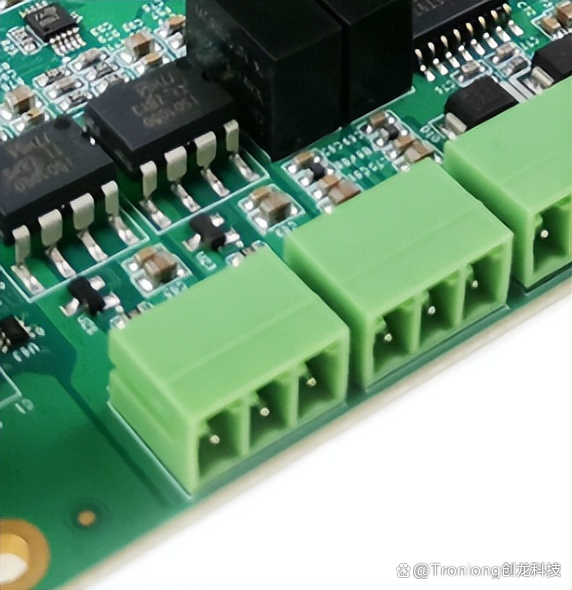

CON9ΪDSP��CANA�ӿڣ�CON10ΪDSP��CANB�ӿڣ��ֱ���DSP��CANA��CANB��������������3pin 3.81mm��ɫ���ӷ�ʽ��

ͼ 44

ͼ 45

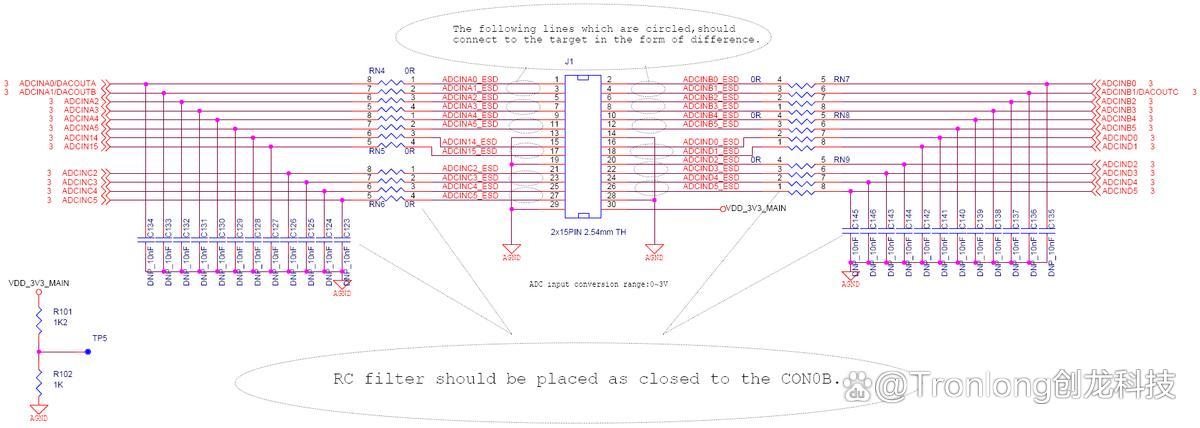

AD/DA�ӿ�

J1ΪAD/DA�ӿڣ�2x 15pin����2.54mm��

ͼ 46

ͼ 47

���ע�����

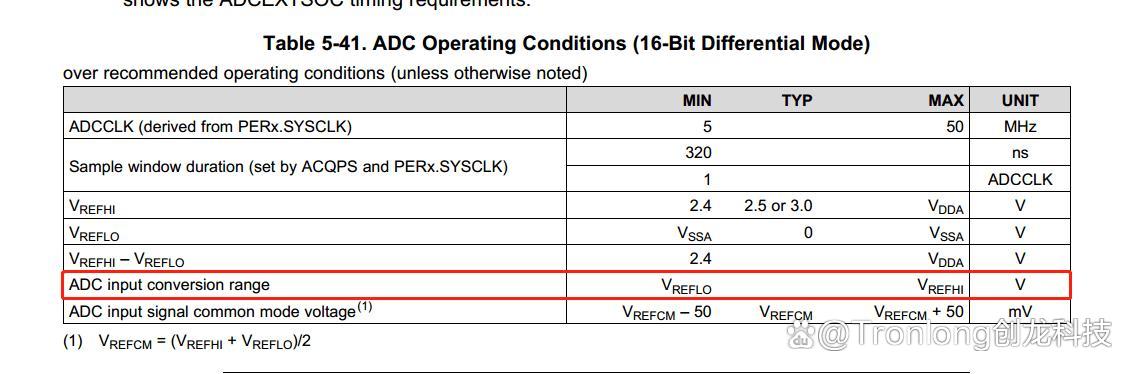

ADC֧��12·���(16bit,1.1MSPS)��24·��������(12bit,3.5MSPS)����ѹ���뷶ΧΪ0 ~ 3.3V��

��ע��ADC�����뷶Χȡ����VREFLO��VREFHI��ֵ��VREFLO�ں��İ��ڲ��ѽӵأ�VREFHI��3V�ο���ѹ��

ͼ 48

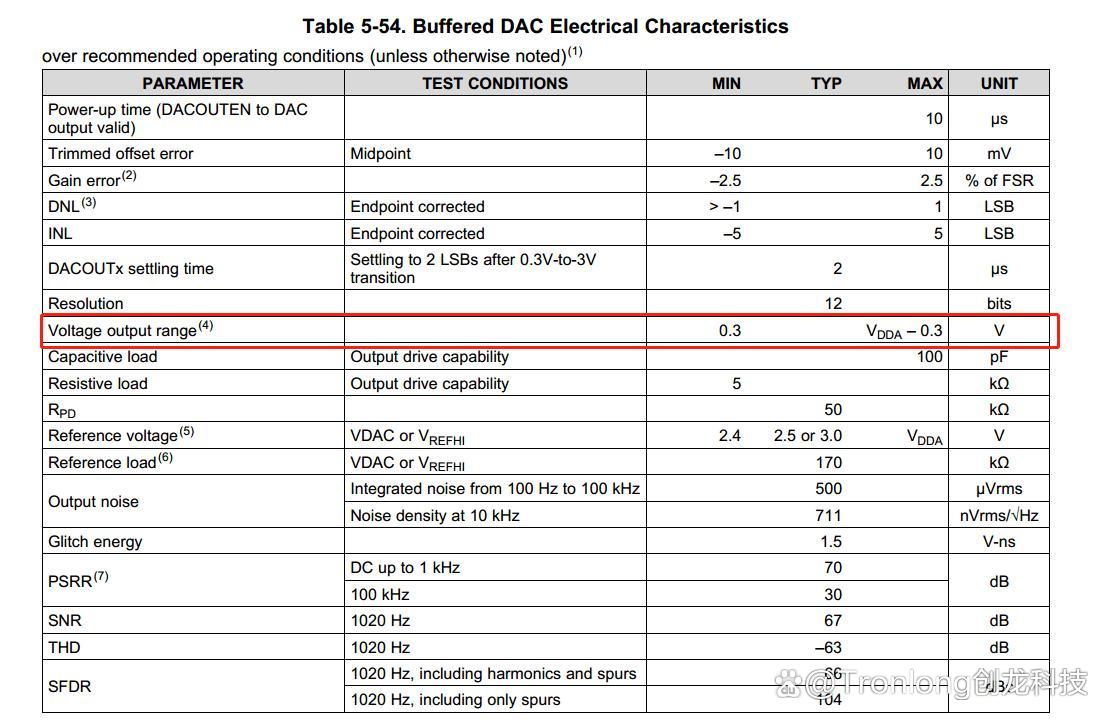

DAC֧��3·12bit DAC�������ѹ�����ΧΪ0.3V ~ 3V��

��ע��DAC��ѹ�����ΧΪ0.3V ~ (VDDA �C 0.3V)��VDDA�ں��İ��ڲ��ѽ�3.3V��Դ��

ͼ 49

ʹ��AD���빦��ʱ������ο������װ���ƣ�����R-C�˲���·��

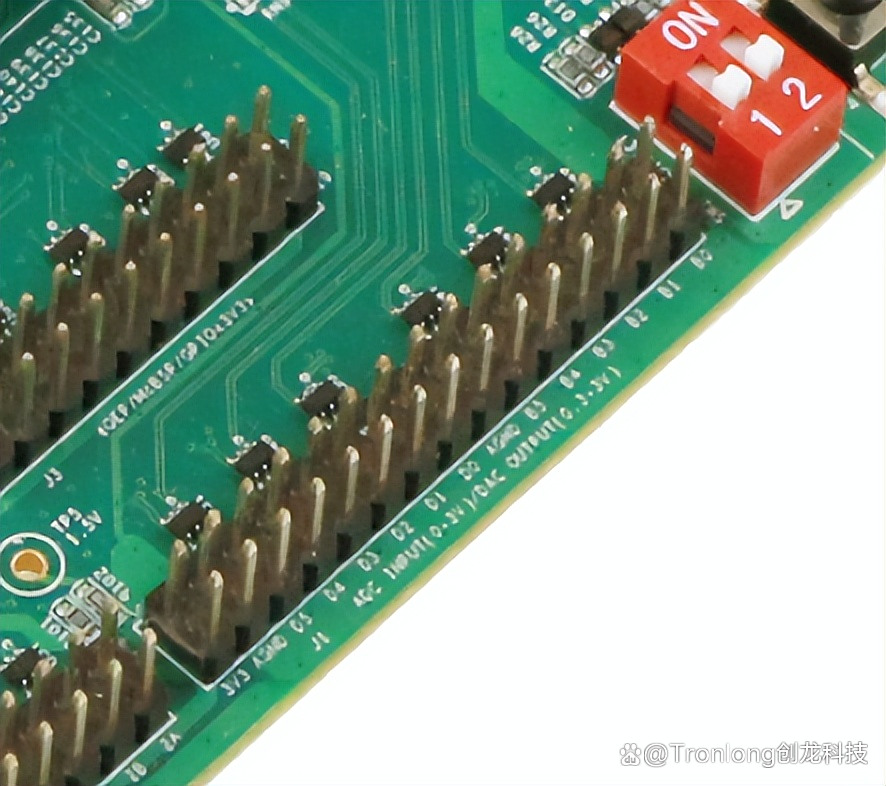

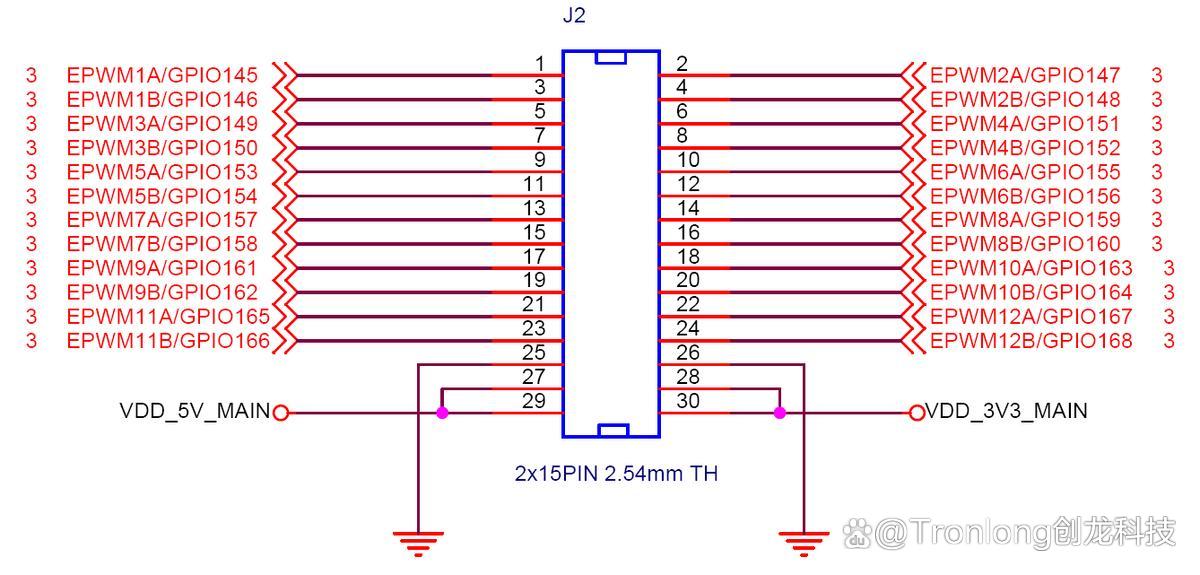

��չIO�źŽӿ�

J2ͨ����������DSP�˵�ePWM/GPIO����չ�źţ�2x 15pin����2.54mm��

ͼ 50

ͼ 51

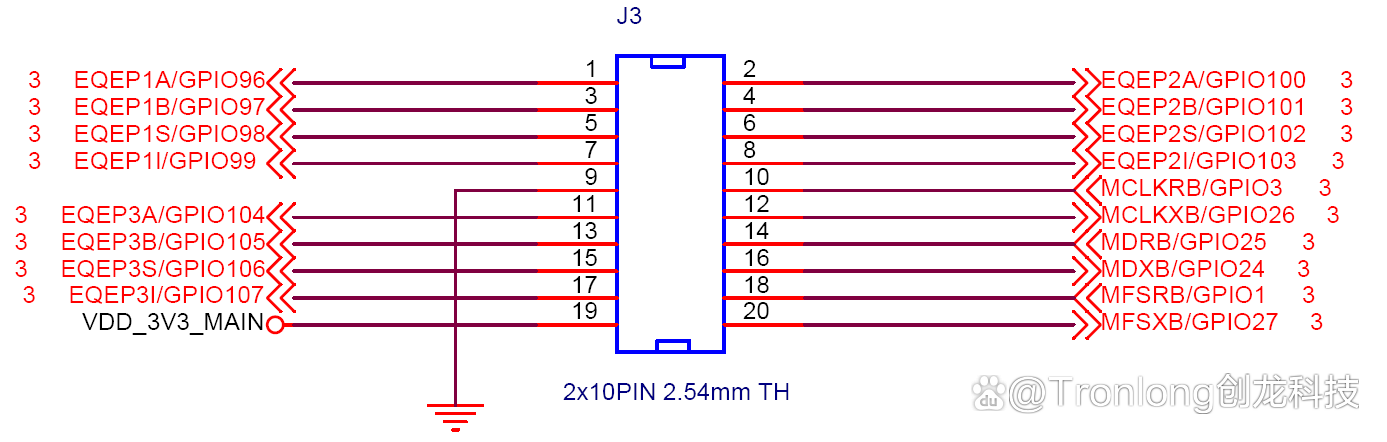

J3ͨ����������DSP�˵�eQEP/McBSP/GPIO����չ�źţ�2x 10pin����2.54mm��

ͼ 52

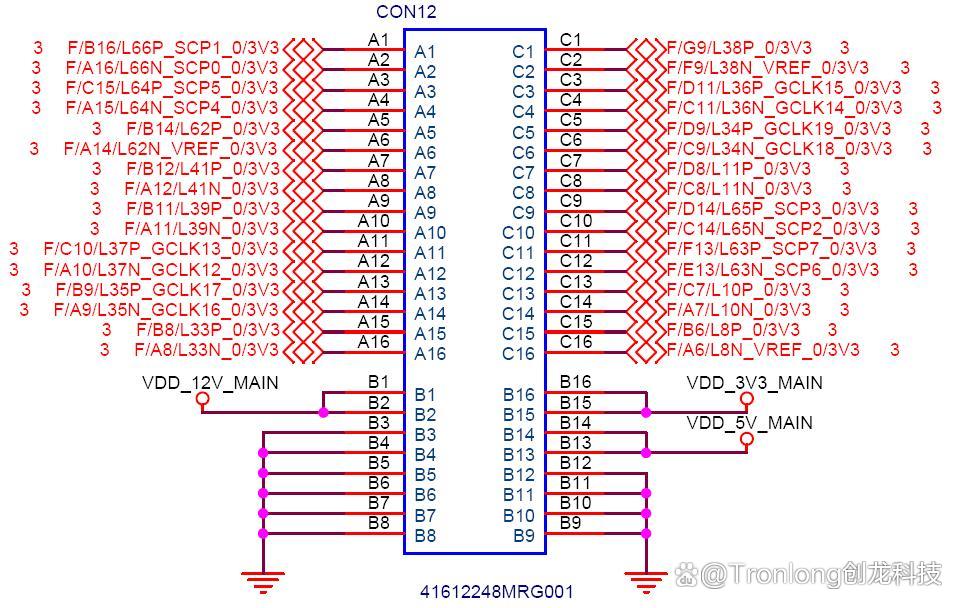

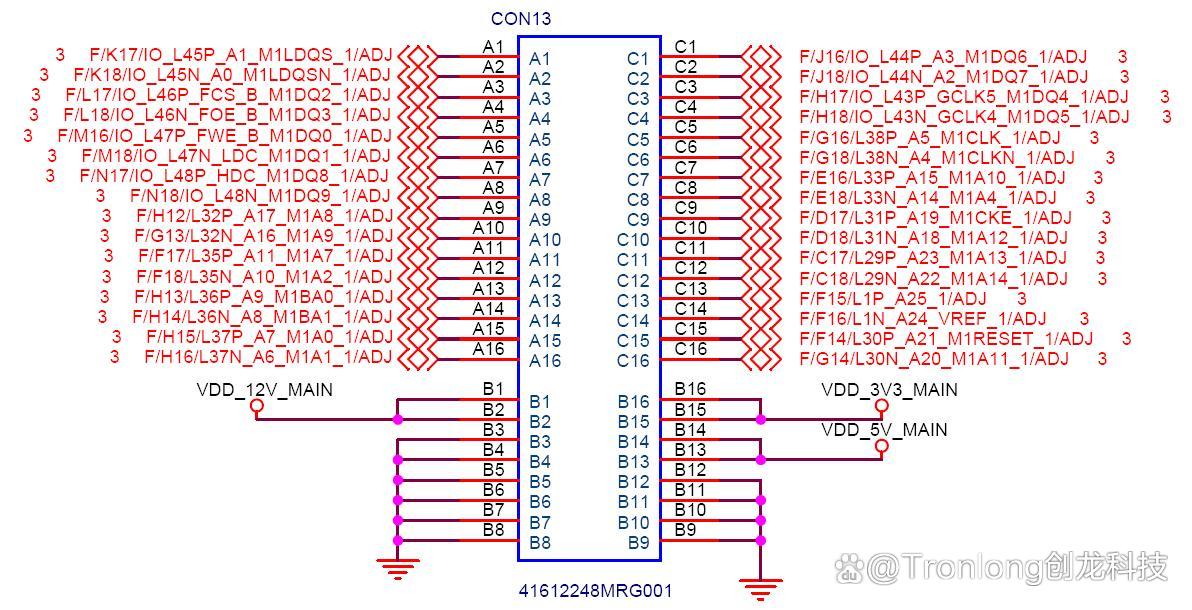

ͼ53CON12��CON13Ϊŷʽ������������48pin�������FPGA�˵�IO��չ�źš�

ͼ 54

ͼ 55

ͼ 56

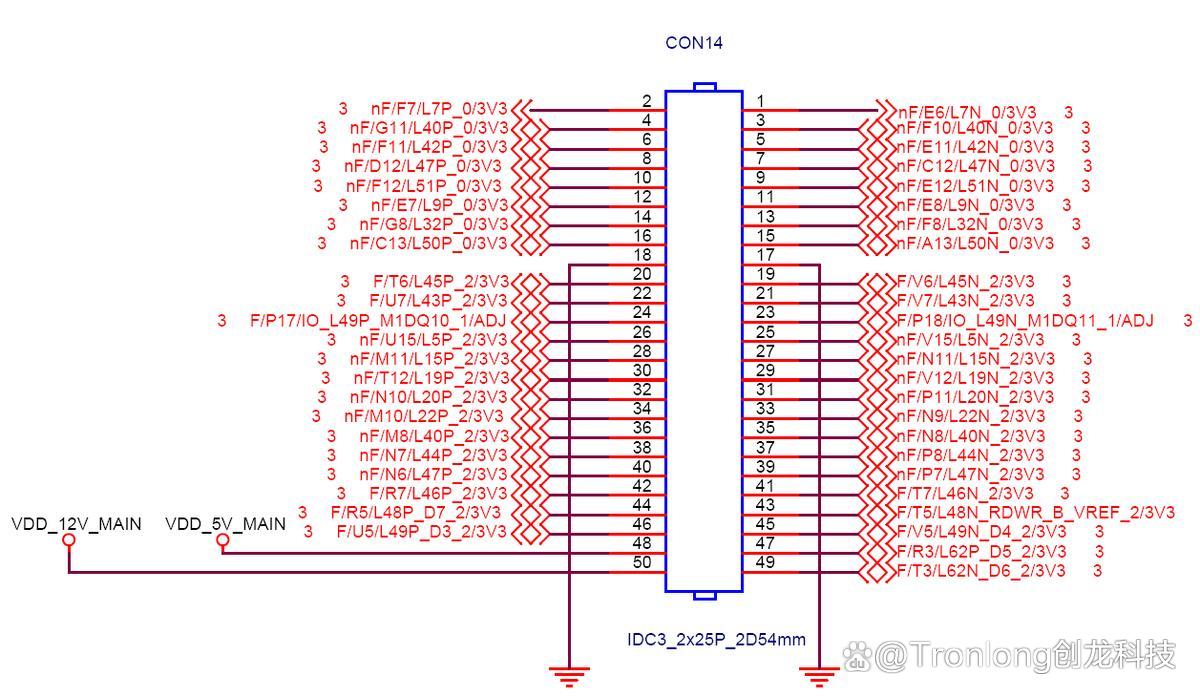

CON14ΪIDC3����ţ������2x 25pin�������FPGA�˵�IO��չ�źš�

ͼ 57

ͼ 58

���ע�����

����ʹ����չ�ӿ���DSP�˵�EMIF1���Ž��ⲿ������������EMIF1���ⲿ����֮�䴮�ӻ�������·����ͨ��EMIF1��Ƭѡ�źŻ�����IO���ƻ�����ʹ�ܣ������ⲿ����Ӱ����İ�����EMIF1���ӵ�SRAM��FPGA�Ķ�д���ܡ�