这一封装技术,要崛起了

2024年05月06日 15:06 发布者:eechina

来源:半导体行业观察据分析机构Yole预计,2028年先进封装市场规模将达786亿美元,2022-2028年的年复合增长约10%,显示出巨大的发展潜力。

其中,扇出型面板级封装(FOPLP)作为先进封装技术发展的一个重要分支,正在频频进入人们的视野。

近日,有消息传出,AI芯片龙头英伟达最快将于2026年导入扇出型面板级封装,借此缓解CoWoS先进封装产能吃紧,导致AI芯片供应不足的问题,英特尔、AMD等半导体大厂后续也将逐步加入扇出型面板级封装的阵营。

这一举动或将打破当下CoWoS在AI芯片先进封装独霸的局面。

AI的风,吹到了FOPLP市场

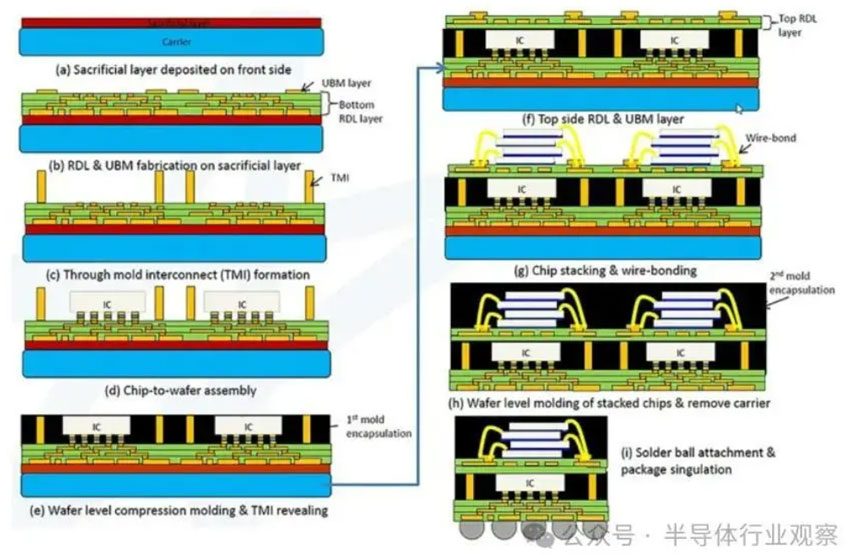

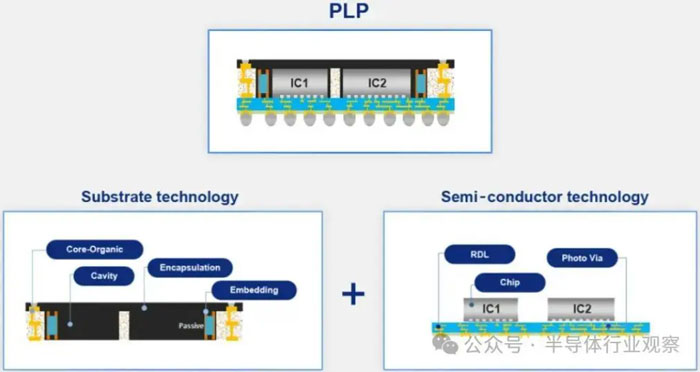

扇出面板级封装是基于重新布线层(RDL)工艺,将芯片重新分布在大面板上进行互连的先进封装技术,能够将多个芯片、无源元件和互连集成在一个封装内。FOPLP与传统封装方法相比,提供了更大的灵活性、可扩展性和成本效益。

扇出型面板级封装可以理解为扇出晶圆级封装的延伸,是在多晶粒集成的需求,加上进一步降低生产成本的考量下,所衍生而出的封装技术。

因此,扇出型板级封装具备显著的效能提升和成本降低优势。其高面积利用率有效减少了浪费,同时能够在一次封装过程中处理更多的芯片,显著提高了封装效率,形成强大的规模效应,从而具有极强的成本优势。

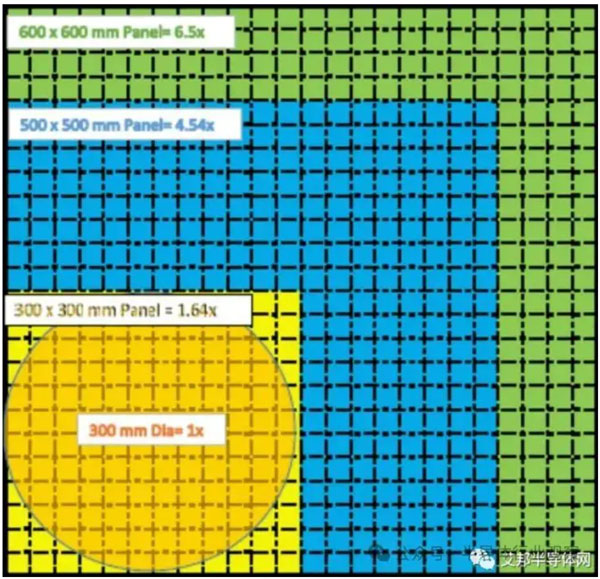

据Yole的报告显示,FOWLP(扇出型晶圆级封装)技术的面积使用率<85%,FOPLP面积使用率>95%,这使得300mmx300mm的面板比同尺寸12英寸的晶圆可以多容纳1.64倍的die,这导致生产过程中生产速率的差异。

晶圆级封装上出现的Partial DIE(Edge缺陷DIE)将不会在面板级封装中出现

(图源:艾邦半导体网)

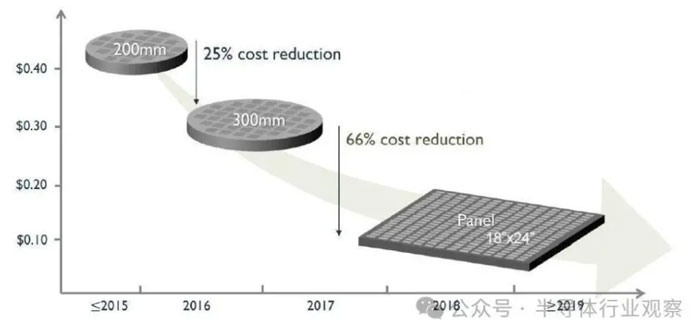

同时,随着基板面积的增加,芯片制造成本逐渐下降。从200mm过渡到300mm大约能节省25%的成本,而从300mm过渡到板级封装,则能节约高达66%的成本。

图源:Yole

综合FOPLP的各项优势来看,英伟达、AMD、英特尔等AI芯片大厂导入扇出型面板级封装,除了希望借此缓解CoWoS先进封装产能吃紧,导致AI芯片供应不足的问题之外。

另一方面,主流厂商也试图尝试利用FOPLP封装技术降低成本,弥补先进制程芯片研发和制造成本不断上升的困难。

苏州晶方半导体副总经理刘宏钧给笔者算了一笔账,以英伟达的H100为例,它是在CoWoS-S(硅基)上封装的7个芯片,中心是814平方毫米的H100 GPU芯片,围绕它的是6个堆叠的HBM内存芯片。H100每季度的出货量高达400000个且供不应求,据报道台积电2023年初的CoWoS产能还不到每月10000片,而到年底可能已经突破了20000片/月,据传台积电会继续增加相关产能至40000片/月,以应对AI芯片大厂的需求。这些产能的80%会被英伟达和AMD消耗,后续随着GB200等新产品的热卖,以及其他厂商例如博通对CoWoS的需求,台积电的产能确实已经有了被挤爆的危险,短时间内不会有任何缓和的迹象。

因此,寻找某种其他的方案来解决产能已经是过去至少一年来行业的共同认知,这确实为FOPLP封装带来了新的机遇。

“由于其工艺尺寸原因,FOPLP技术指标弱于台积电的CoWoS-S,但其潜在优势是成本和产能瓶颈突破的可能性。这些因素促使目前CoWoS的用户努力寻找替代技术。” 刘宏钧补充道。

尽管弱于CoWoS技术,但相较于其它传统封装技术,FOPLP以其卓越的I/O密度和电气性能,成为满足AI计算需求的关键所在。

通过RDL工艺,FOPLP技术能够实现高带宽、高密度的D2D互连,这一特性在AI计算中尤为关键,能够有效满足数据传输与处理的迫切需求。

不仅如此,FOPLP技术在提升芯片功能密度、缩短互联长度以及进行系统重构等方面均展现出显著优势,这恰好符合AI时代对芯片性能提出的基本要求。

图源:未来半导体

芯和半导体联合创始人代文亮博士表示,从人工智能发展的需求和走势来看,高性能计算芯片引入面板级扇出型封装技术是大致确定的路线选择。尽管该技术短期内无法替代CoWoS,但未来在封测市场的份额比重会逐步增加,以解决当前有机基板和硅基板接近极限,无法满足高端芯片需求的瓶颈问题。

综合来看,AI计算的需求增长、先进封装技术的发展、成本效益的考量、技术创新的推动、市场需求的多样化等,这些因素共同促成了FOPLP技术的异军突起。

据Yole数据显示,2022年FOPLP的市场空间大约是11.8亿美元,预计到2026年将增长到43.6亿美元。可以预见,FOPLP技术具备巨大的成长潜力。

“嗅到” FOPLP商机

广阔的市场前景下,OSAT、IDM、Foundry、基板制造商等一众厂商,都已“嗅到”商机,近年来都在积极投入发展FOPLP这一先进封装技术,进一步证明了市场对FOPLP技术的广泛认可和高度期待。

根据麦姆斯咨询早些时候发布的报告显示,三星电子、力成科技、日月光、群创、华润微、奕斯伟、中科智芯、Nepes和云天半导体等正在利用现有设施和工艺能力,投资面扇出型板级封装技术,以实现规模经济生产。

以三星电子为例,2015在与台积电竞争Apple手机处理器订单失利后,三星电子对先进封装技术给予了高度关注,其成立的特别工作小组携手三星电机成功开发出面板等级扇出封装技术,并与台积电研发的InFO-WLP技术一较高下,成为第一家进入量产的面板级封装厂商。

图源:三星

这一努力在2018年实现了一个新的里程碑,三星在其Galaxy智能手表上采用了最新的扇出型面板级封装APE-PMIC,这是FOPLP的全球首次量产。

最初,FOPLP主要用于移动应用。2020年开始的5G、AI、自动驾驶和服务器需求导致对模块化和高速数据处理的需求急剧增长。

因此,兼顾性能和成本驱动优势的FOPLP技术可以满足多芯片封装方面的这些需求,已经逐渐拓展到诸多应用领域。

刘宏钧向笔者指出:“高端扇出封装需求主要来自于同时需要晶体管数量和通讯带宽的应用领域,例如FPGA、某些Networking管理芯片等。由于I/O密度,良率和成本的因素,这些扇出封装一般都是以Chip-last的形式存在。除了这些高端扇出封装外,还有一些中低端的扇出以Chip-first的形式存在,以实现更高密度的封装集成,应用在例如Sensor、射频芯片、电源芯片、WiFi/音频等产品上。”

值得关注的是,如汽车中约有66%的芯片可以使用FOPLP封装技术进行生产,是汽车芯片生产的出色解决方案。

在此趋势带动下,力成、群创、日月光等上述厂商逐渐结合自身的工艺能力投资扇出型板级封装技术的量产。同时国内一些IDM、封装厂也开始提前布局FOPLP。

例如,力成科技在2018年打造了全球第一座使用扇出型面板级封装制程的量产基地,正式布局高阶封装领域,已成功运用于联发科PMIC和音频收发器上。

图源:Powertech Technology

日月光也是最早布局面板级扇出型技术的领导厂家之一。于2019 年底产线建置完成,2020 下半年量产,应用在RF、FEM、Power和Server领域。2022年日月光推出了VIPack先进封装平台,提供垂直互联集成封装解决方案。VIPack就是以3D异质整合为关键技术的先进互连技术解决方案,建立完整的协同合作平台。

群创光电首度提出一项前所未有的概念――Panel Semiconductor,以业界超大尺寸G3.5 FOPLP (620mm X 750mm) Glass Panel,开发线宽介于2μm-10μm的中高阶半导体封装,为客户提供更有竞争力的技术和利润价值。

在头部大厂的带动下,中国大陆扇出面板级封装厂商正在乘胜追击,已经量产或具备生产能力。

中科四合:深圳中科四合致力于为AI、通信、汽车、工业、消费类等多个领域提供高性能、高可靠性的功率芯片及模组解决方案。中科四合是国内最早将大板级扇出封装(FOPLP)技术量产于功率芯片/模组的供应商之一,公司产品涵盖多种二极管、MOSFET、GaN、电源模组等功率芯片/模组。中科四合在深圳龙华区和厦门海沧区均设有制造工厂,2017年已规模量产。针对功率芯片及模组产品定义,中科四合基于基板湿法工艺全新开发了一套板级扇出封装工艺和生产线,可实现低成本、高散热、大电流、三维集成、低寄生参数的功率芯片/模组解决方案。

奕成科技:奕成科技是国内板级高密封装技术领域的领先者,主要从事板级系统封测集成电路业务,载板尺寸为510mmx 515mm,技术平台可对应2D FO、2.xD、3D PoP、Embedded Die四大板级系统集成技术方案,在芯片偏移控制、翘曲度、RDL等核心工艺指标上已达行业领先水准。2023年4月,奕成科技高端板级系统封测集成电路项目点亮投产,标志着其首座板级高密系统封测工厂正式进入客户认证及批量试产阶段。

矽磐微电子:华润微电子于2018年成立矽磐微电子(重庆)公司从事面板级封装业务,面板级封装技术有效解决了Chiplet封装成本高昂的问题,更适用于功率类半导体封装异构集成化。

矽迈微电子:合肥矽迈微电子建成了国内首条具备量产能力的基板扇出封装生产线,并率先完成工艺开发,客户认证和试验量产,量产产品包括电源管理类,射频类,系统模块等。

佛智芯微电子:广东佛智芯微电子结合现有半导体制程工艺设备和后道载板制程工艺装备的优势,打造了半加成法扇出封装先进的线路创成工艺(i-FOSATM),具备工艺先进 、成本合理、供应链安全的特性,建设国内首条高性价比板级扇出型封装研发线和示范线,旨在打通Chip-First、Chip-Last、3D/SiP核心工艺。同时,为增加板级封装技术创新与合作,佛智芯通过建立“板级扇出封装创新联合体”,打造产业链共性平台,联合体成员包含亚智、华为、华进等40多名国内外企业。

天芯互联:天芯互联为深南电路全资子公司,同样拥有FOPLP平台,为客户提供高集成小型化的半导体器件模组封装解决方案和半导体测试接口解决方案。

...

此外,扇出型面板级封装发展还需要更多厂商的参与和投入:

在面板级封装光刻机领域,日本佳能动作非常快,佳能在错失超紫外光刻机的机遇后,不会再放过任何一个机会。

在面板级封装RDL工艺领域,Manz是领跑者之一,2016年Manz开始进军半导体先进封装领域,面板尺寸目前已能做到业界最大的700mm x 700mm面板,并克服了面板翘曲问题。

在面板级晶粒贴装领域,ASMPT、华封科技、华芯智能、深科达等都有相应产品,基本可以满足大多数封装产品的需求。

另外,考虑到芯片、封装与PCB的同步设计及同步研发越来越重要,FOPLP的发展也需要PCB厂、载板厂、面板厂等这些后段封装厂的协同努力。一方面有助于上述企业利用既有经验快速切入FOPLP技术,另一方面,前后段半导体产业的共同投入也有助于寻找到最具竞争力的生产成本、提升产品竞争力的路径。

对PCB厂、载板厂来说,发展FOPLP的优势是通过制程知识和设备升级、改造,逐渐向前段制程跨进,快速跨入先进封装技术市场。

而处于半导体产业链上游的EDA,同样也在密切关注FOPLP行业的变化与市场机会。代文亮博士指出,在EDA方面,芯和半导体能够为FOPLP封装设计提供一站式多物理场仿真EDA解决方案,通过完全自主知识产权,大规模跨尺度的仿真引擎,AI加持的自适应网格剖分和分布式并行计算等核心能力,帮助用户解决信号完整性、电源完整性、电磁兼容、电热和盈利给可靠性等方面的问题,加速产品开发和迭代。

无论如何,随着产业链上下游厂商的不断关注和入局,有望推动扇出型面板级封装市场空间的进一步增长。

FOPLP封装,仍挑战重重

尽管FOPLP封装技术开始崭露头角,业界已有厂商实现了FOPLP产品的量产。

但总体来说,目前FOPLP产业的发展还不够成熟,因受到良率产量、供应链不完善、面板翘曲及设备投入研发、标准化问题、散热等种种挑战,整个行业尚处于相对早期的阶段,产业发展进程仍有待提高。

以设备为例,由于面板级封装是全新的封装技术,也需要新的封装设备加以支持。比如贴片机就是产线改造中最重要的环节之一。由于面板级封装使用的载板尺寸更大,表面容易凹凸翘曲,对应机台尺寸也就更大,Pick & Place动作的路径更长,对机台的效率、运动机构的一致性、稳定性都提出了更高的要求。

此外,面板级封装与当前晶圆级封装数据系统不完全兼容,需要对原有产线进行改造。面板级封装还需要RDL制造设备,开发特殊的检测及测量工具以及激光/热释放层、介质层材料等,这需要大量的前期投资来打造完整的产业生态链。这也是为什么台积电、英特尔至今也没有大肆开发扇出型面板级封装。

有专家指出,面板级封装设备的开发需要厂商在硬件和算法上具有较强的协同能力,这样才能从底层上去解决问题。

另外,面板级封装设备厂商还应具有一定的模块化平台架构设计能力,这样才能使设备产品具有高度灵活性和可转换性,做到全工艺、全尺寸覆盖,帮助客户更好地适应先进封装领域快速的发展变化,产能可快速在不同工艺需求的产线进行调配,工艺转换成本也更低。

板级封装的难点还在于设备供应商没有统一规范,面板尺寸没有通用标准。主要原因是因为当前需求量还较低,设备供应商没有太大的热情来冒险开发整条产线。

总的来说,要想充分释放FOPLP这一技术的潜力,行业必须正视并克服贴装精度、芯片偏移、翘曲和光刻等诸多挑战,对设备和标准的持续投资与发展亦不可或缺。

市场份额上,过去数年FOPLP一直处于爬坡阶段,在整体封装市场占比较小。

但相信随着英伟达、AMD、英特尔等芯片大厂的转向,未来将有望充分释放FOPLP封装的技术优势和市场需求,为行业发展注入新动力。