星嵌OMAPL138+国产FPGA工业开发板 中科亿海微 EQ6HL45系列FPGA 替代spartan-6

2023年10月12日 20:22 发布者:CoreKernel

1 评估板简介[*]基于TI OMAP-L138(定点/浮点DSP C674x+ARM9)+ FPGA处理器的开发板;

[*]OMAP-L138是TI德州仪器的TMS320C6748+ARM926EJ-S异构双核处理器,主频456MHz,高达3648MIPS和2746MFLOPS的运算能力;

[*]FPGA采用中科亿海微eHiChip 6家族EQ6HL45系列芯片,或Xilinx Spartan-6系列芯片XC6SL16,可升级至XC6SL45。(亿海芯EQ6HL45 CSG324 pin-to-pin Xilinx Spartan-6系列XC6SLX9、XC6SLX16、XC6SLX25、XC6SLX45);

[*]TI OMAP-L138作为主处理器,实现操作系统运行、算法处理、指令控制等功能;

[*]FPGA作为协处理器,实现并行采集、外部信号处理、接口转换等功能;

[*]OMAP-L138和FPGA通过EMIF、SPI或UPP等接口通信,通信速度可高达228MByte/s;

[*]开发板引出丰富的外设,包含1路CAN、2路RS485(其中1路RS485/422复用)、2路RS232、2路网口(1路百兆、1路千兆)、1路ADC、2路DAC、数码管、SATA、TF/SD、USB OTG、4个USB 1.1 HOST、UART、RTC、LCD等接口,同时也引出MCASP、MCBSP、uPP、SPI、EMIFA、I2C等接口,方便用户扩展。

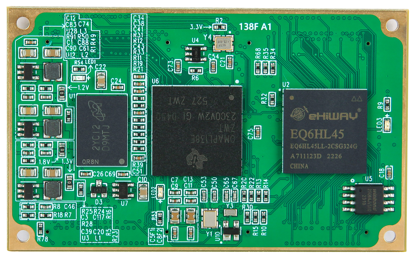

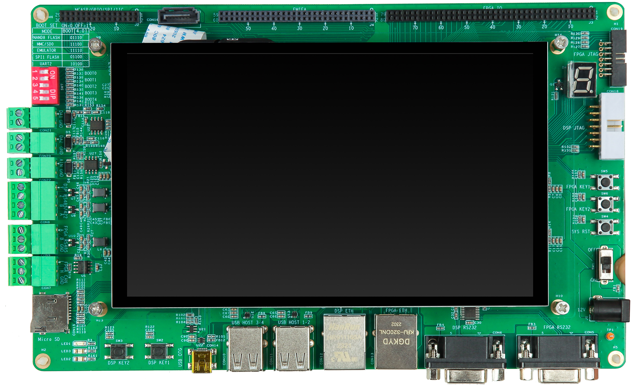

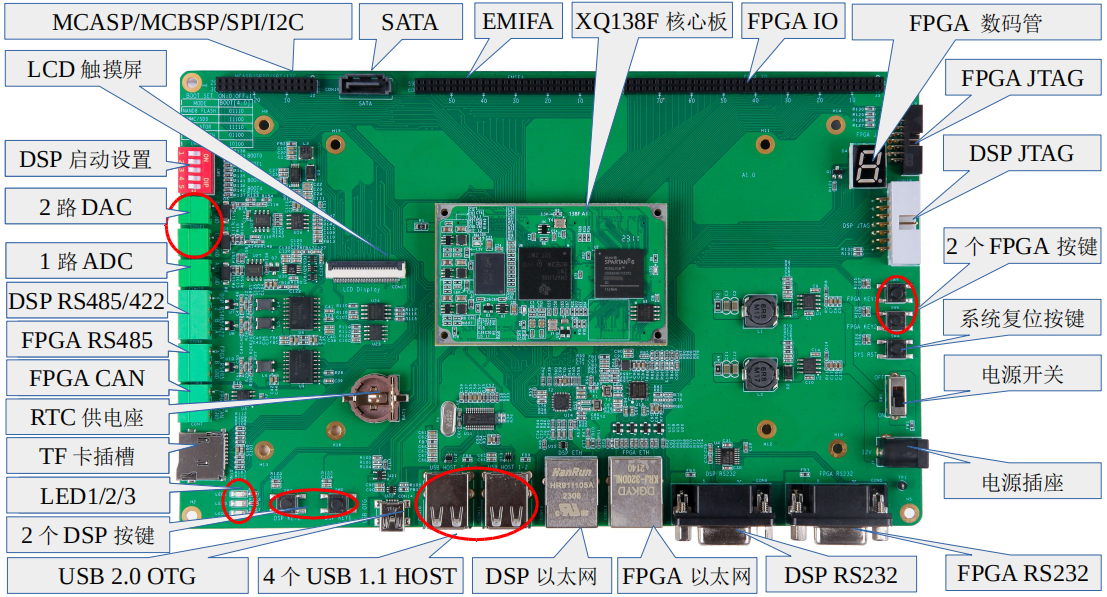

图1 OMAP-L138 + EQ6HL45系列图2 OMAP-L138 + Spartan-6

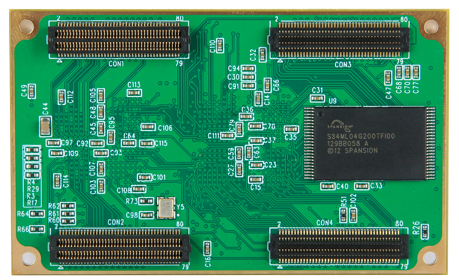

图3 核心板背面图

图3 核心板背面图  图4 L138 + EQ6HL45正面图

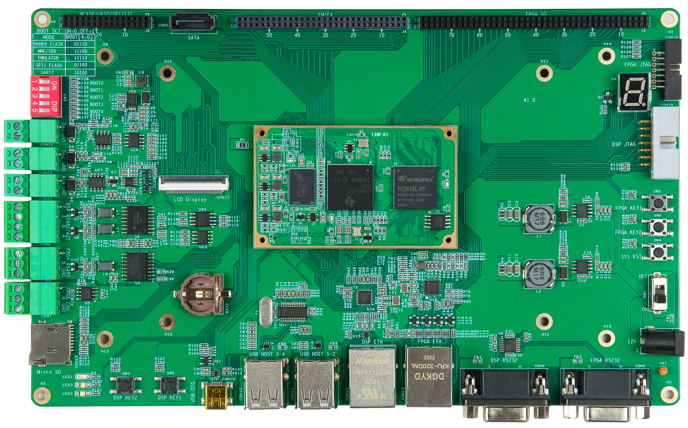

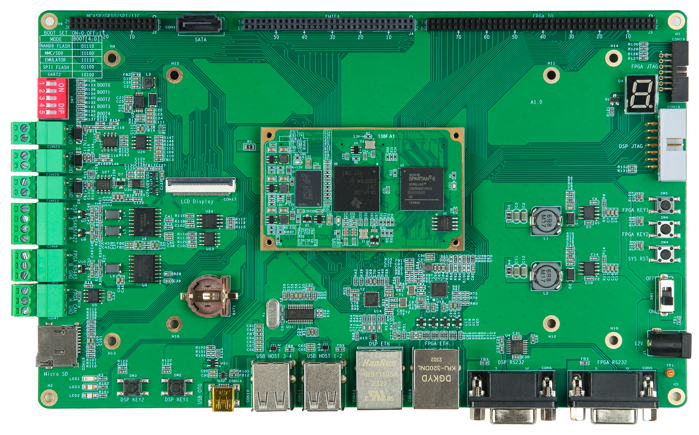

图4 L138 + EQ6HL45正面图  图5 L138 + Spartan-6正面图

图5 L138 + Spartan-6正面图  图6 开发板正面图

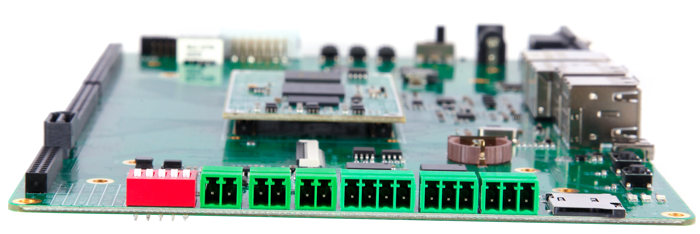

图6 开发板正面图  图7 开发板侧视图

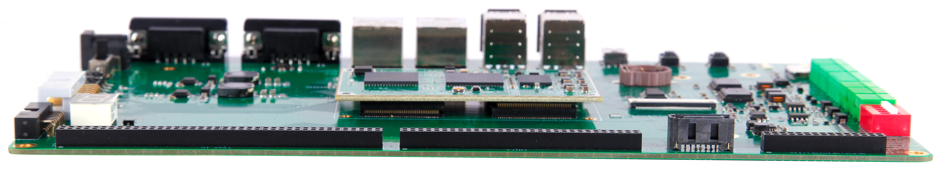

图7 开发板侧视图  图8 开发板侧视图

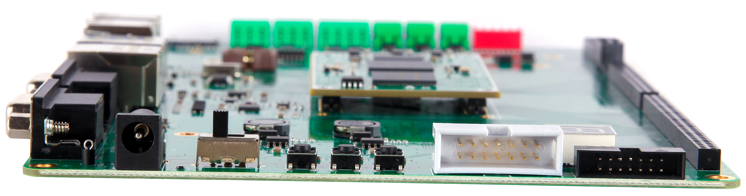

图8 开发板侧视图  图9 开发板侧视图

图9 开发板侧视图  图10 开发板侧视图 XQ138F-EVM是广州星嵌电子科技有限公司基于SOM-138F核心板(OMAP-L138+FPGA)开发的DSP+ARM+FPGA三核开发板,采用沉金无铅工艺的4层板设计,它为用户提供了SOM-XQ138F核心板的测试平台,用于快速评估SOM-XQ138F核心板的整体性能。SOM-XQ138F引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层应用,大大降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。不仅提供丰富的Demo程序,还提供详细的开发教程,全面的技术支持,协助客户进行底板设计、调试以及软件开发。用户可以进行项目前期的验证和评估,也可以直接用来开发自己的产品。 2 典型应用图像处理设备工业控制 智能电力系统 手持检测仪器音视频数据处理高精度仪器仪表数据采集处理显示系统中高端数控系统通信设备 医疗电子设备惯性制导... 3 软硬件参数

图10 开发板侧视图 XQ138F-EVM是广州星嵌电子科技有限公司基于SOM-138F核心板(OMAP-L138+FPGA)开发的DSP+ARM+FPGA三核开发板,采用沉金无铅工艺的4层板设计,它为用户提供了SOM-XQ138F核心板的测试平台,用于快速评估SOM-XQ138F核心板的整体性能。SOM-XQ138F引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层应用,大大降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。不仅提供丰富的Demo程序,还提供详细的开发教程,全面的技术支持,协助客户进行底板设计、调试以及软件开发。用户可以进行项目前期的验证和评估,也可以直接用来开发自己的产品。 2 典型应用图像处理设备工业控制 智能电力系统 手持检测仪器音视频数据处理高精度仪器仪表数据采集处理显示系统中高端数控系统通信设备 医疗电子设备惯性制导... 3 软硬件参数  图11 开发板硬件资源框图

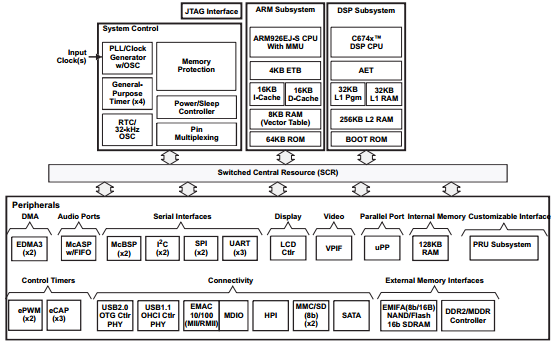

图11 开发板硬件资源框图  图12 OMAP-L138资源图

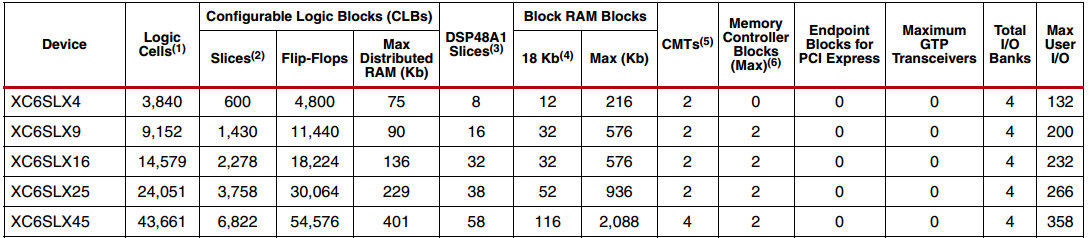

图12 OMAP-L138资源图  图13 Xilinx Spartan-6 FPGA基础参数

图13 Xilinx Spartan-6 FPGA基础参数  图14 亿海神针系列FPGA产品表

图14 亿海神针系列FPGA产品表  图15 亿海芯系列FPGA的基础参数 3.1 硬件性能表1

图15 亿海芯系列FPGA的基础参数 3.1 硬件性能表1 CPUTI OMAPL138(TMS320C6748+ARM926EJ-S),频率最高达456M

FPGA(2选1)(Pin-To-Pin)中科亿海微eHiChip 6家族EQ6HL45LL-2CSG324G

或Xilinx Spartan-6系列XC6SLX16/XC6SLX45

内存RAM128MB工业级DDR2(256MB可选)

存储ROM512MB工业级NAND FLASH,用于DSP存储

64Mb工业级SPI FLASH,用于FPGA配置

B2B连接器2个80pin 0.5mm间距的母座,2个80 pin 0.5mm间距的公座

DSP仿真器接口1个14Pin JTAG接口

FPGA调试接口1个14Pin JTAG接口

SATA接口1个7pin SATA硬盘接口

RJ45网口OMAPL138端1个10/100M bps自适应RJ45网络接口

FPGA端1个10/100/1000M bps自适应RJ45网络接口

RTC1个RTC供电座,使用3.3V纽扣电池供电

按键1个DSP复位按键

2个DSP GPIO按键

2个FPGA IO按键

显示1个LCD触摸屏接口,0.5mm间距,40Pin

启动设置1个5bit的拨码开关,用于OMAPL138启动选择

USB4个USB 1.1 HOST接口,通过USB HUB扩展实现

1个USB 2.0 OTG接口

UARTRS232 1个DSP RS232电平的串口,DB9母座

1个FPGA RS232电平的串口,DB9母座

RS485/4221个DSP RS485/422电平的串口(复用)

1个FPGA RS485电平的串口

CAN1个FPGA CAN接口

ADC1路ADC 精度12-bit;输入电压范围0~10V;采样率500KSPS

DAC2路DAC精度12-bit,数字编码值范围0~4095;输出电压范围:①0~8.192V(x1增益模式,支持所有数字编码(0~4095)),②0~13.2V(x2增益模式,由于DAC限制输出不能超过VDD,故只支持部分编码(0~3300,十六进制值0~CE4),编程时需要注意);输出稳定时间:4.5us;用户接口:SPI接口,SPI时钟最高20MHz。

TF/SD1个TF/SD卡插槽

LED核心板(3个) 1个红色的LED电源指示灯LED1;1个DSP LED灯LED2;1个FPGA LED灯LED3;

底板(3个)1个红色的LED电源指示灯LED1;1个DSP LED灯LED2;1个FPGA LED灯LED3;

FRAM1片铁电存储器,存取速度比E2PROM更快,写操作之前无需先擦除

数码管1个8段高亮数码管

测试点1个接地柱,用于示波器接地,方便信号测量

拓展IO30pin 2.0间距的母座1个,引出MCASP,MCBSP,SPI,I2C等扩展信号

60pin 2.0间距的母座1个,引出EMIFA

80pin 2.0间距的母座1个,引出FPGA IO 74个

扩展接口上提供 12V、5V 供电,方便扩展外设供

电源开关1个拨动电源开关

电源接口1个DC电源插座,外径5.5mm,内径2.1mm

3.2 软件参数 表2

ARM端软件支持裸机、Linux3.3

DSP端软件支持裸机、SYS/BIOS操作系统

CCS版本号CCS7.4

FPGA端软件(2选1)亿灵思软件(eLinx)

ISE14.7(Spartan-6)

图形界面开发工具Linux下支持Qt界面开发

双核通信支持裸机(中断+共享内存)、DSPLINK 、SYSLINK

软件开发包DVSDK、MCSDK