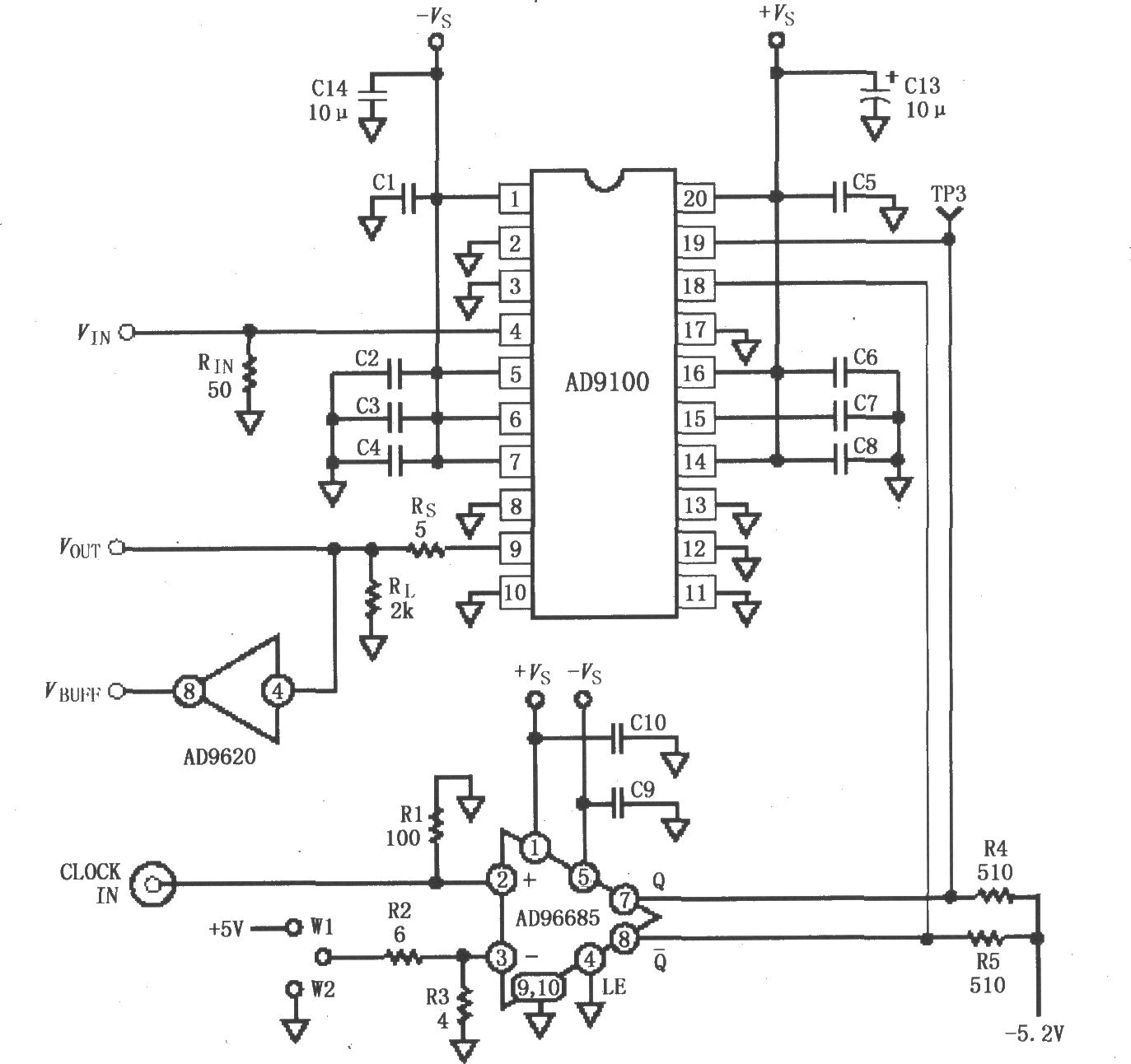

采样保持放大器AD9100接口的测试板电路

2011年04月18日 10:54 发布者:circuit_share

如图所示为AD9100接口的测试板电路。信号VIN输入AD9100的4脚,保持电容和开关内置在器件内,信号经过采样保持放大后由9脚直接输出,也可以经过AD9620缓冲级后输出。时钟输人“CLOCK IN”加到模拟器件公司的超快比较器AD96685的同相输入端,Q、Q非输出后送到AD9100的CLK和CLK非(19、18脚),作为采样保持控制信号。C1~Cl0采用0.01μF电容器,C13、Cl4采用钽电容器。连接W1时为TTL时钟信号,连接W2时为地参考信号。