运放电源去耦旁路措施

2011年03月01日 10:33 发布者:circuit_share

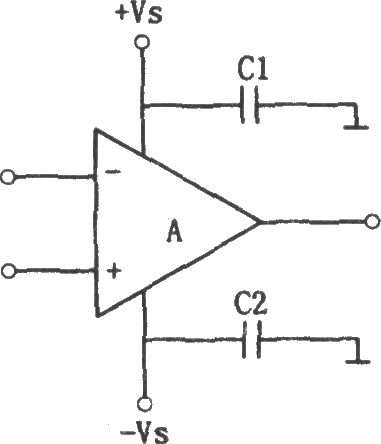

每个集成运放的电源引线,一般都应采用去耦旁路措施,即从电源引线端到地跨接一个高性能的电容,如图所示。图中的高频旁路电容,通常可选用高频性能优良的陶瓷电容,其值约为0.1μF。或采用lμF的钽电容。这些电容的内电感值都较小。在运放的高速应用时,旁路电容C1和C2应接到集成运放的电源引脚上,引线尽量短,这样可以形成低电感接地回路。当所使用的放大器的增益带宽乘积大于10MHz时,应采用更严格的高频旁路措施,此时应选用射频旁路电容,如0.1μF圆片陶瓷电在,同时每个印刷板或每4~5个集成芯片再增加一对(C1和C2)钽电容。对于通用集成芯片,对旁路的要求不高,但也不能忽视,通常最好每4~5个器件加一套旁路电容。不论所用集成电路器件有多少,每个印刷板都要至少加一套旁路电容。