玩转Zynq连载4――AXI总线协议介绍2

2019年05月10日 16:20 发布者:rousong1989

玩转Zynq连载4――AXI总线协议介绍2 更多资料共享 链接:https://share.weiyun.com/5s6bA0s 2 信号描述2.1 全局信号表2-1 全局信号

玩转Zynq连载4――AXI总线协议介绍2 更多资料共享 链接:https://share.weiyun.com/5s6bA0s 2 信号描述2.1 全局信号表2-1 全局信号信号来源描述

ACLK时钟源全局时钟信号。所有的信号都在全局时钟的上升沿采样。

ARESETn复位源全局复位信号。低电平有效。

2.2 写地址通道信号表2-2 写地址通道信号

信号来源描述

AWID主机写地址ID。这个信号是写地址信号的唯一标识。

AWADDR主机写地址。写地址总线为突发写传输的第一个有效数据传输提供地址。相关控制信号决定了后续传输的有效数据相对于第一个地址的关系。

AWLEN主机突发长度。突发长度提供突发传输的数据长度。

AWSIZE主机突发位宽。突发位宽提供突发传输中每个有效数据的位宽。

AWBURST主机突发类型。突发类型伴随着位宽信息。

AWLOCK主机锁定类型。

AWCACHE主机缓存类型。

AWPROT主机保护类型。

AWVALID主机写地址有效。这个信号指示此时传输的是有效的写地址和控制信息:1 = 地址和控制信息是有效的;0 = 地址和控制信息无效。地址和控制信息保持稳定直到地址响应信号AWREADY为高电平。

AWREADY从机写地址准备好。这个信号指示从机已经准备好接收地址和相关的控制信号:1 = 从机准备好;0 = 从机未准备好。

注:对于一般的应用,AWBURST、AWLOCK、AWCACHE和AWPROT通常赋一个特定的值,即设定为固定的工作模式即可。 2.3 写数据通道信号表2-3 写数据通道信号

信号来源描述

WID主机写ID。这个信号是写数据传输的唯一表示。WID值必须与写传输的AWID值匹配。

WDATA主机写数据。写数据总线可以是8、16、32、64、128、256、512或1024bits带宽。

WSTRB主机写数据有效字节数。这个信号指明写数据的每个字节数据是否写入到最终的地址中。在写数据总线中每8bit有一个WSTRB位相对应,指示该信号写入的数据字节是否更新到最终的写地址中。

WLAST主机最后一个数据写入指示信号。这个信号高电平时,表明一次突发写传输的最后一个数据正在传输。

WVALID主机写有效信号。这个信号指明写数据有效:1 = 写数据有效;0 =写数据无效。

WREADY从机写准备好。这个信号指明从机可以接收写数据:1 = 从机准备好;0 = 从机未准备好。

2.4 写响应通道信号表2-4 写响应通道信号

信号来源描述

BID从机响应ID。这是写响应的唯一标识。BID值必须与写传输的AWID值匹配。

BRESP从机写响应。这个信号表明写传输的状态。可用的状态是OKAY,EXOKAY,SLVERR,和DECERR。

BVALID从机写响应有效信号。这个信号表明写响应是有效的:1 = 写响应有效;0 = 写响应无效。

BREADY主机响应准备好。这个信号表明主机可以接收响应信息。1 = 主机是准备好的;0 = 主机未准备好。

2.5 读地址通道信号表2-5 读地址通道信号

信号来源描述

ARID主机读地址ID。这个信号是读地址信号的唯一标识。

ARADDR主机读地址。读地址总线提供一个突发读传输的初始地址。只提供了突发读传输的起始地址,其余读数据的地址通过控制信号可以计算出来。

ARLEN主机突发长度。突发长度提供了突发读传输的数据个数。

ARSIZE主机突发位宽。这个信号指示了突发传输的数据位宽。

ARBURST主机突发类型。

ARLOCK主机锁定类型。

ARCACHE主机缓存类型。

ARPROT主机保护类型。

ARVALID主机写地址有效。这个信号为高电平时,写地址和控制信息有效,并将保持稳定,直到地址响应信号ARREADY拉高。1 = 地址和控制信息有效;0 = 地址和控制信息无效。

ARREADY从机写地址准备好。这个信号表明从机准备好接收地址和相关的控制信号:1 = 从机准备好;0 = 从机未准备好。

2.6 读数据通道信号表2-6 读数据通道信号

信号来源描述

RID从机读ID标签。这个信号是读数据的唯一标识。RID值是由从机产生的,必须与读地址通道传输的ARID值相匹配。

RDATA从机读数据。读数据总线可以是8、16、32、64、128、256、512或1024bits带宽。

RRESP从机读响应。这个信号表明读传输的状态。可用的反馈状态是OKAY,EXOKAY,SLVERR和DECERR。

RLAST从机最后一个读数据有效标志位。这个信号表明一次突发读传输的最后一个数据正在传输。

RVALID从机读有效信号。这个信号表明读数据有效,1 = 读数据有效;0 = 读数据无效。

RREADY主机读数据准备好。这个信号表明主机可以接收从机送出的读数据:1 = 主机是准备好的;0 = 主机未准备好。

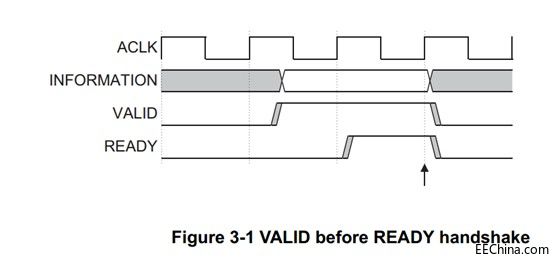

3 握手过程 全部5个通道使用同样的VALID和READY握手机制来实现数据和控制信息的传输。这个双向的流控制机制使主机和从机能控制数据和控制信息的传输速度。发送端产生VALID信号指示数据或控制信息有效,接收端产生READY信号表明它可以或已经接收数据或控制信息。只有在VALID和READY信号都为高电平的时候才能进行有效的传输。 如图所示,这是一个握手的实例。发送端送出数据或控制信息(INFORMATION),并将VALID信号拉高。来自发送端的数据或控制信息保持稳定直到接收端将READY信号拉高,指明接收端已经接收数据或控制信息。箭头表明了传输实际发生的时机。

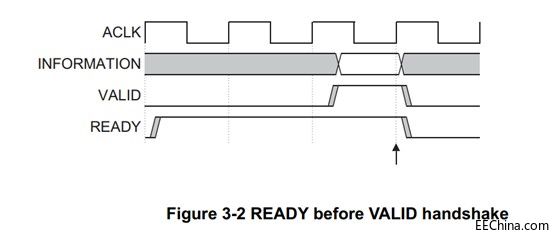

必须注意,若发送端要发起一次传输,不允许VALID信号一直等待READY变为高电平才执行拉高操作。正确的操作应该是,将VALID拉高,一直保持高电平直到READY拉高,完成一个完整的握手操作。 如图所示,接收端在VALID信号拉高之后,才将READY信号拉高,表示发送端发出的数据或控制信息被接收。这意味着,接收端若在VALID信号拉高之前就已经将READY拉高表示准备好,那么只需要1个时钟周期就可以完成一次数据或控制信息的有效传输。箭头表明传输发生的时机。

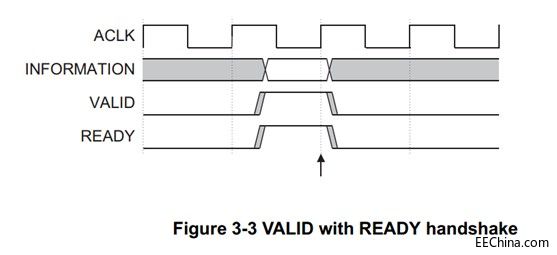

必须注意,若发送端要发起一次传输,不允许VALID信号一直等待READY变为高电平才执行拉高操作。正确的操作应该是,将VALID拉高,一直保持高电平直到READY拉高,完成一个完整的握手操作。 如图所示,接收端在VALID信号拉高之后,才将READY信号拉高,表示发送端发出的数据或控制信息被接收。这意味着,接收端若在VALID信号拉高之前就已经将READY拉高表示准备好,那么只需要1个时钟周期就可以完成一次数据或控制信息的有效传输。箭头表明传输发生的时机。 接收端送出的READY信号在VALID拉高之后才拉高,在这个握手机制中是允许的。如果READY为高电平,在VALID拉高之前将READY拉低也是允许的。如图所示,在这个实例中,VALID和READY信号同一个时钟周期拉高了,那么这正好是一次有效的数据或控制信息的传输。

接收端送出的READY信号在VALID拉高之后才拉高,在这个握手机制中是允许的。如果READY为高电平,在VALID拉高之前将READY拉低也是允许的。如图所示,在这个实例中,VALID和READY信号同一个时钟周期拉高了,那么这正好是一次有效的数据或控制信息的传输。  更多资料共享 链接:https://share.weiyun.com/5s6bA0s

更多资料共享 链接:https://share.weiyun.com/5s6bA0s