玩转Zynq连载2――Zynq PS的GPIO外设

2019年04月18日 16:37 发布者:rousong1989

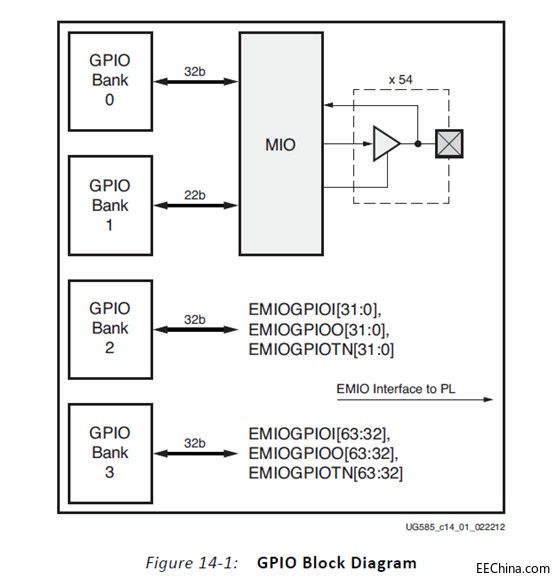

玩转Zynq连载2――Zynq PS的GPIO外设 更多资料共享 链接:https://share.weiyun.com/5s6bA0s 1 概述 Zynq的GPIO外设控制最多54个MIO引脚,也可以通过EMIO接口连接到PL(最多支持64个输入引脚或128个输出引脚)。GPIO外设可以分为4个Bank。 GPIO外设的主要特性如下: ● 54个GPIO信号通过MIO引脚引出。 ● 192个GPIO信号通过EMIO接口连接到PL引脚引出(64个输入引脚;128个输出引脚,其中64个实际输出引脚和64个输出使能引脚)。 ●每个GPIO都可以独立编程为输入、输出或中断接口。 ● 使能信号、位或bank为单位的数据写入操作、方向控制信号。 ● 每个GPIO都有可编程的中断控制 GPIO的功能框图如下所示。

1 概述 Zynq的GPIO外设控制最多54个MIO引脚,也可以通过EMIO接口连接到PL(最多支持64个输入引脚或128个输出引脚)。GPIO外设可以分为4个Bank。 GPIO外设的主要特性如下: ● 54个GPIO信号通过MIO引脚引出。 ● 192个GPIO信号通过EMIO接口连接到PL引脚引出(64个输入引脚;128个输出引脚,其中64个实际输出引脚和64个输出使能引脚)。 ●每个GPIO都可以独立编程为输入、输出或中断接口。 ● 使能信号、位或bank为单位的数据写入操作、方向控制信号。 ● 每个GPIO都有可编程的中断控制 GPIO的功能框图如下所示。 GPIO外设分为4个Bank。 ● Bank0由32位的MIO引脚pin组成。 ● Bank1由22位的MIO引脚pin组成。 ● Bank2由32位EMIO信号EMIO组成。 ● Bank3由32位EMIO信号EMIO组成。 2 GPIO内部结构 GPIO内部结构如图所示。

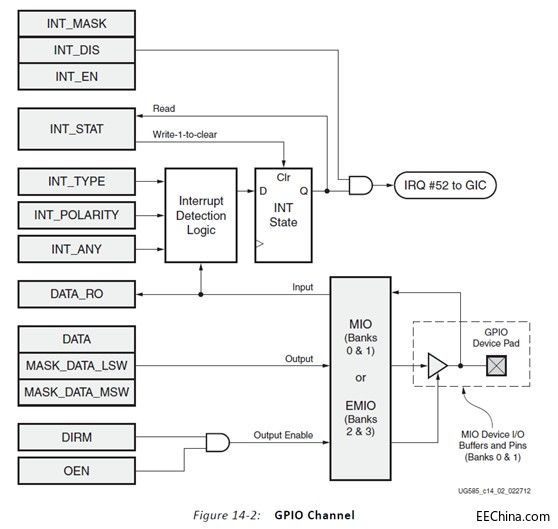

GPIO外设分为4个Bank。 ● Bank0由32位的MIO引脚pin组成。 ● Bank1由22位的MIO引脚pin组成。 ● Bank2由32位EMIO信号EMIO组成。 ● Bank3由32位EMIO信号EMIO组成。 2 GPIO内部结构 GPIO内部结构如图所示。 GPIO可以被配置为输入或输出信号。DATA_RO寄存器能够反馈当前GPIO的输入(OE信号为低)或输出(OE信号为高)状态值。通过MASK_DATA寄存器的设置,可以实现对一个bank中特定一个或多个GPIO的控制。 其它几个主要寄存器的功能如下。 ● DATA寄存器。当GPIO配置为输出时,该寄存器用于配置GPIO的输出电平值。该寄存器一次性写入所有32个GPIO的输出值;读取该寄存器时,返回的是写入的电平状态,并不一定是实际的电平状态。 ● MASK_DATA_LSW寄存器。该寄存器用于屏蔽不需要更新的DATA寄存器的低16位。 ● MASK_DATA_MSW寄存器。该寄存器用于屏蔽不需要更新的DATA寄存器的高16位。 ● DIRM寄存器。方向控制寄存器。该寄存器用于控制GPIO的输入输出方向。高电平表示输出,低电平表示输入。 ● OEN寄存器。输出使能。当GPIO配置为输出引脚,该寄存器有效。高电平表示输出使能,低电平表示输出关闭。 更多资料共享 链接:https://share.weiyun.com/5s6bA0s

GPIO可以被配置为输入或输出信号。DATA_RO寄存器能够反馈当前GPIO的输入(OE信号为低)或输出(OE信号为高)状态值。通过MASK_DATA寄存器的设置,可以实现对一个bank中特定一个或多个GPIO的控制。 其它几个主要寄存器的功能如下。 ● DATA寄存器。当GPIO配置为输出时,该寄存器用于配置GPIO的输出电平值。该寄存器一次性写入所有32个GPIO的输出值;读取该寄存器时,返回的是写入的电平状态,并不一定是实际的电平状态。 ● MASK_DATA_LSW寄存器。该寄存器用于屏蔽不需要更新的DATA寄存器的低16位。 ● MASK_DATA_MSW寄存器。该寄存器用于屏蔽不需要更新的DATA寄存器的高16位。 ● DIRM寄存器。方向控制寄存器。该寄存器用于控制GPIO的输入输出方向。高电平表示输出,低电平表示输入。 ● OEN寄存器。输出使能。当GPIO配置为输出引脚,该寄存器有效。高电平表示输出使能,低电平表示输出关闭。 更多资料共享 链接:https://share.weiyun.com/5s6bA0s