勇敢的芯伴你玩转Altera FPGA连载90:FPGA片内ROM FIFO RAM联合实例

2018年09月07日 22:22 发布者:rousong1989

勇敢的芯伴你玩转Altera FPGA连载90:FPGA片内ROM FIFO RAM联合实例特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD

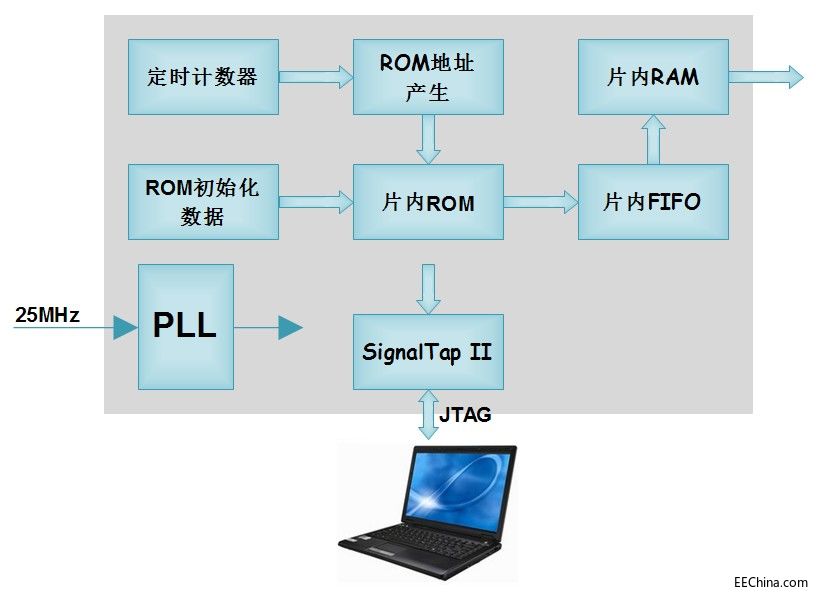

功能概述 该工程实例内部系统功能框图如图9.89所示。我们通过IP核分别例化了ROM、FIFO和RAM,ROM有预存储的数据可供读取,将其放入FIFO中,随后再读出送到RAM供读取。通过Quartus II集成的在线逻辑分析仪SignalTapII,我们可以观察FPGA片内ROM、FIFO和RAM的读写时序,也可以只比较ROM预存储的数据和RAM最后读出的数据,确认整个读写缓存过程中,数据的一致性是否实现。

功能概述 该工程实例内部系统功能框图如图9.89所示。我们通过IP核分别例化了ROM、FIFO和RAM,ROM有预存储的数据可供读取,将其放入FIFO中,随后再读出送到RAM供读取。通过Quartus II集成的在线逻辑分析仪SignalTapII,我们可以观察FPGA片内ROM、FIFO和RAM的读写时序,也可以只比较ROM预存储的数据和RAM最后读出的数据,确认整个读写缓存过程中,数据的一致性是否实现。 图9.89 存储器联合实例功能框图 本实例工程模块层次如图9.90所示。

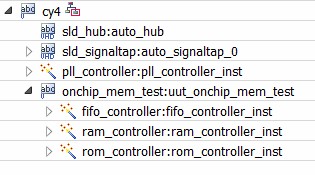

图9.89 存储器联合实例功能框图 本实例工程模块层次如图9.90所示。 图9.90 存储器联合实例模块层次 功能仿真Quartus II中,点击菜单“Tools à Run Simulation Tool à RTL Simulation”进行仿真。接着,Modelsim中我们可以查看读FIFO的波形。 ROM、FIFO和RAM读写波形如图9.92所示。

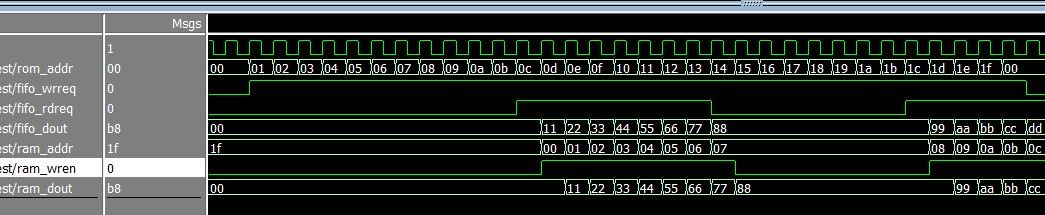

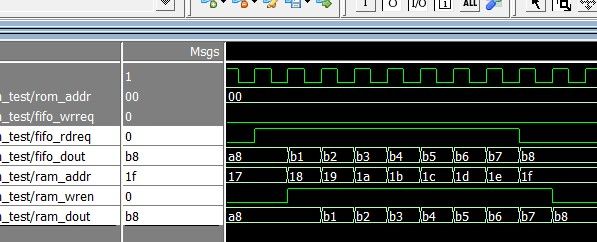

图9.90 存储器联合实例模块层次 功能仿真Quartus II中,点击菜单“Tools à Run Simulation Tool à RTL Simulation”进行仿真。接着,Modelsim中我们可以查看读FIFO的波形。 ROM、FIFO和RAM读写波形如图9.92所示。 图9.92 ROM、FIFO和RAM读写波形 ROM读数据波形如图9.93所示。

图9.92 ROM、FIFO和RAM读写波形 ROM读数据波形如图9.93所示。 图9.93 ROM读数据波形 FIFO第一次读波形如图9.94所示。

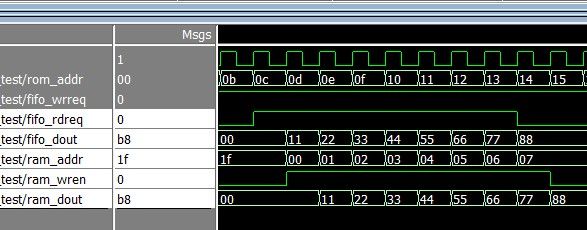

图9.93 ROM读数据波形 FIFO第一次读波形如图9.94所示。 图9.94 第一次FIFO读数据波形 FIFO第二次读波形如图9.95所示。

图9.94 第一次FIFO读数据波形 FIFO第二次读波形如图9.95所示。 图9.95 第二次FIFO读数据波形 FIFO第三次读波形如图9.96所示。

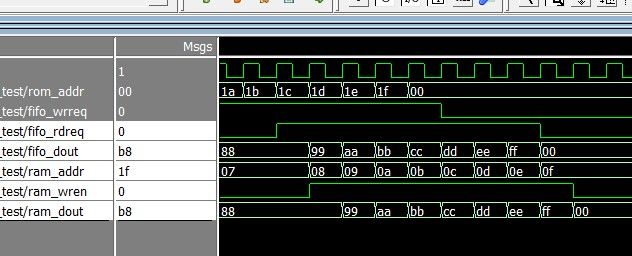

图9.95 第二次FIFO读数据波形 FIFO第三次读波形如图9.96所示。 图9.96 第三次FIFO读数据波形 FIFO第四次读波形如图9.97所示。

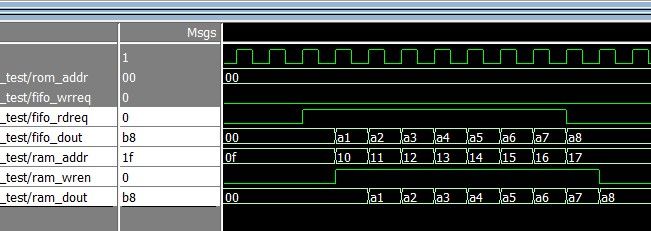

图9.96 第三次FIFO读数据波形 FIFO第四次读波形如图9.97所示。 图9.97 第四次FIFO读数据波形 RAM读数据波形如图9.98所示。

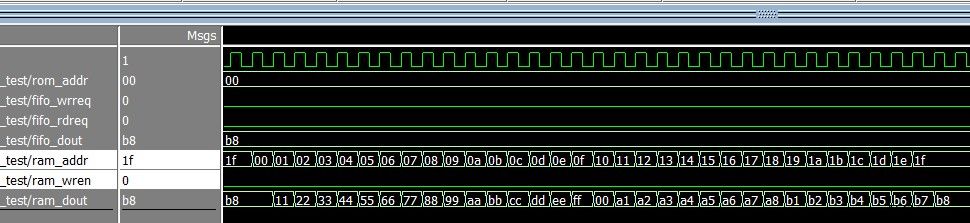

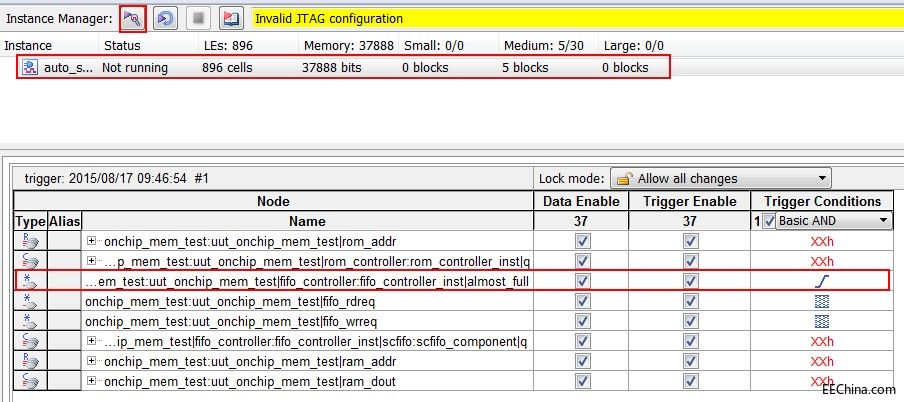

图9.97 第四次FIFO读数据波形 RAM读数据波形如图9.98所示。 图9.98 RAM读数据波形 在线调试 连接好下载线,给CY4开发板供电。点击菜单“Tools à SignalTap II Logic Analyzer”,进入逻辑分析仪主页面。在右侧的“JTAG ChinaConfiguration”窗口中,建立好USB Blaster的连接后,点击“SOF Manager”后面的Programmer按钮进行下载。 如图9.99所示,在“trigger”下面罗列了我们已经添加好的需要观察的信号,尤其是在almost_full信号的TriggerConditions一列,我们设置了值上升沿,表示almost_full上升沿(FIFO快要满了)时我们将触发采集。另外,我们用鼠标点击选中Instance下面的唯一一个选项,然后单击InstanceManager后面的运行按钮,执行一次触发采集。

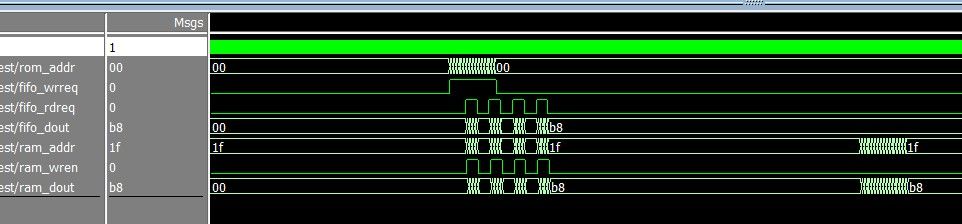

图9.98 RAM读数据波形 在线调试 连接好下载线,给CY4开发板供电。点击菜单“Tools à SignalTap II Logic Analyzer”,进入逻辑分析仪主页面。在右侧的“JTAG ChinaConfiguration”窗口中,建立好USB Blaster的连接后,点击“SOF Manager”后面的Programmer按钮进行下载。 如图9.99所示,在“trigger”下面罗列了我们已经添加好的需要观察的信号,尤其是在almost_full信号的TriggerConditions一列,我们设置了值上升沿,表示almost_full上升沿(FIFO快要满了)时我们将触发采集。另外,我们用鼠标点击选中Instance下面的唯一一个选项,然后单击InstanceManager后面的运行按钮,执行一次触发采集。 图9.99 波形采样触发设置波形如图9.100所示。这里包括了ROM的读取操作、FIFO的写和读操作、RAM的写和读操作。

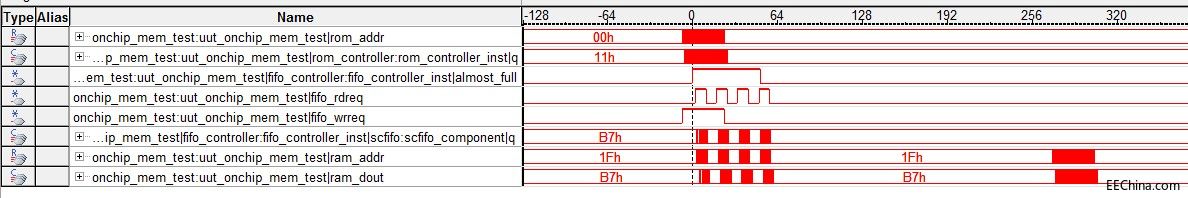

图9.99 波形采样触发设置波形如图9.100所示。这里包括了ROM的读取操作、FIFO的写和读操作、RAM的写和读操作。 图9.100 ROM、FIFO和RAM读写波形

图9.100 ROM、FIFO和RAM读写波形