勇敢的芯伴你玩转Altera FPGA连载85:FPGA片内RAM实例之RAM配置

2018年07月17日 22:21 发布者:rousong1989

勇敢的芯伴你玩转Altera FPGA连载85:FPGA片内RAM实例之RAM配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 在RAM的第一个配置页面中(即“ParameterSettings à Widths/Blk Type/Clks”页面),如图所示进行配置,这里设置RAM的位宽为8bits,深度为32个words。其他设置如图9.41使用默认设置。

在RAM的第一个配置页面中(即“ParameterSettings à Widths/Blk Type/Clks”页面),如图所示进行配置,这里设置RAM的位宽为8bits,深度为32个words。其他设置如图9.41使用默认设置。 图9.41 RAMWidths/Blk Type/Clks配置页面 如图9.42所示,第二个配置页面(即“ParameterSettings à Regs/Clken/Byte Enable/Aclrs”页面)勾选“’q’ output port”。

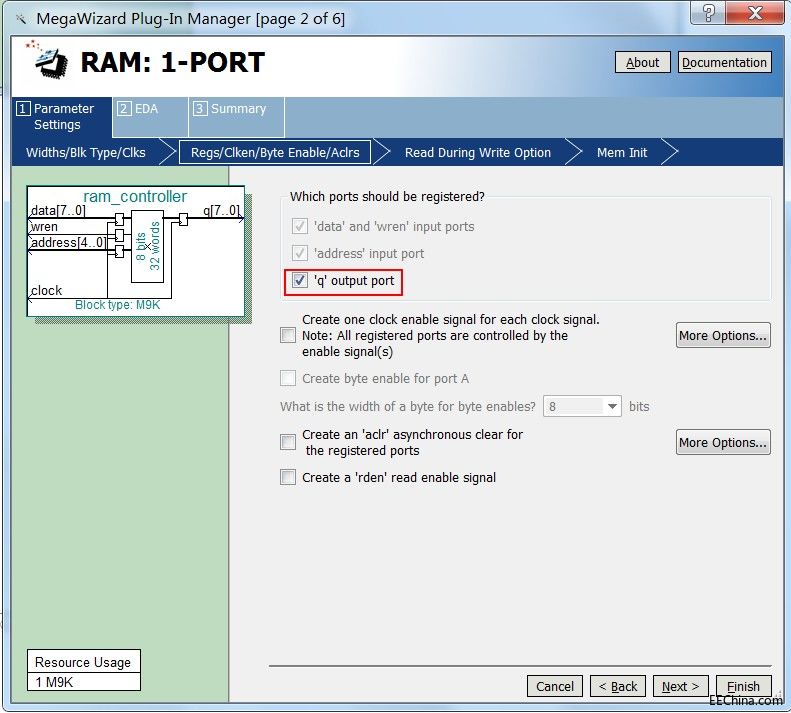

图9.41 RAMWidths/Blk Type/Clks配置页面 如图9.42所示,第二个配置页面(即“ParameterSettings à Regs/Clken/Byte Enable/Aclrs”页面)勾选“’q’ output port”。 图9.42 RAM Regs/Clken/Byt Enable/Aclrs配置页面 其他几个页面使用默认设置,最后我们在Summary页面中,如图9.43所示,确保勾选上ram_controller_inst.v文件的选项,该文件是这个IP核的例化模板。

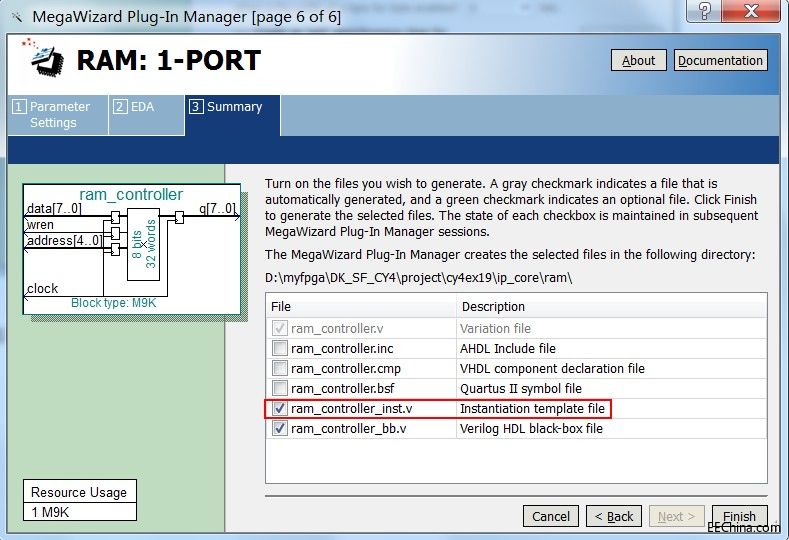

图9.42 RAM Regs/Clken/Byt Enable/Aclrs配置页面 其他几个页面使用默认设置,最后我们在Summary页面中,如图9.43所示,确保勾选上ram_controller_inst.v文件的选项,该文件是这个IP核的例化模板。 图9.43 RAMSummary配置页面 点击“Finish”完成IP核的配置。 如图9.44所示,我们可以在文件夹“…/ip_core/ram”下查看生产的IP核相关源文件。

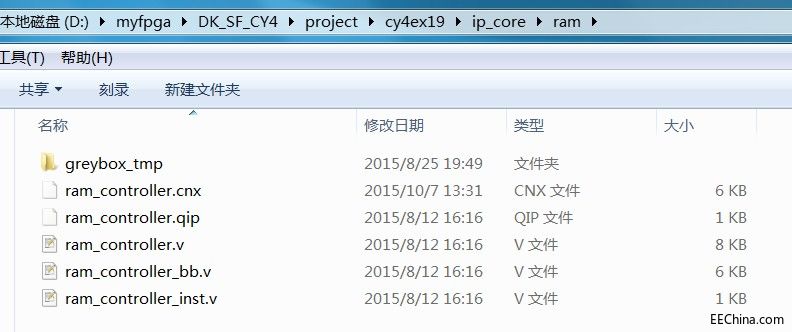

图9.43 RAMSummary配置页面 点击“Finish”完成IP核的配置。 如图9.44所示,我们可以在文件夹“…/ip_core/ram”下查看生产的IP核相关源文件。 图9.44 RAM IP源文件所在文件夹 例化模板ram_controller_inst.v打开如图9.45所示,复制到工程源码中,对“( )”内的“*_sig”信号接口更改并做好映射,就可以将其集成到我们的设计中。

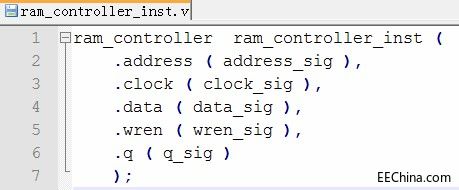

图9.44 RAM IP源文件所在文件夹 例化模板ram_controller_inst.v打开如图9.45所示,复制到工程源码中,对“( )”内的“*_sig”信号接口更改并做好映射,就可以将其集成到我们的设计中。 图9.45 RAM IP核例化模板 如图9.46代码所示,在我们的设计中,我们将RAM的时钟(clock)、地址(address)、写入数据(data)、写数据使能信号(wren)和读出数据(q)分别映射连接。

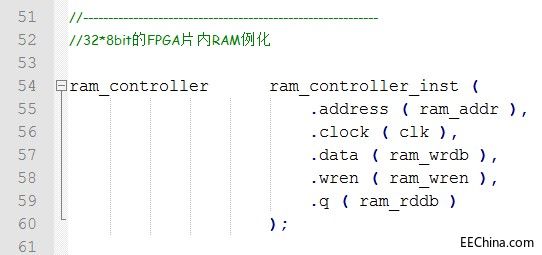

图9.45 RAM IP核例化模板 如图9.46代码所示,在我们的设计中,我们将RAM的时钟(clock)、地址(address)、写入数据(data)、写数据使能信号(wren)和读出数据(q)分别映射连接。 图9.46 RAM IP核在实际代码中的例化

图9.46 RAM IP核在实际代码中的例化