勇敢的芯伴你玩转Altera FPGA连载82:FPGA片内ROM实例之功能仿真与在线调试

2018年06月27日 20:08 发布者:rousong1989

勇敢的芯伴你玩转Altera FPGA连载82:FPGA片内ROM实例之功能仿真与在线调试特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD Quartus II工程中,点击菜单“Tools à Run Simulation Tool à RTL Simulation”进行仿真。当然了,在这之前,这个工程的仿真测试脚本以及在Quartus II中的设置都已经就绪了。 接着,如图9.31、图9.32和图9.31所示,Modelsim中我们可以查看读ROM的波形。

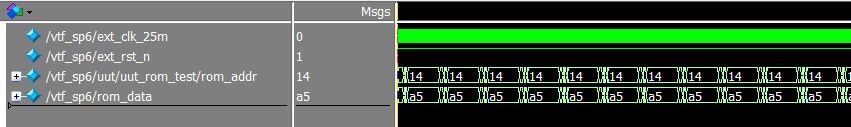

Quartus II工程中,点击菜单“Tools à Run Simulation Tool à RTL Simulation”进行仿真。当然了,在这之前,这个工程的仿真测试脚本以及在Quartus II中的设置都已经就绪了。 接着,如图9.31、图9.32和图9.31所示,Modelsim中我们可以查看读ROM的波形。 图9.31 ROM仿真波形1

图9.31 ROM仿真波形1 图9.32 ROM仿真波形2

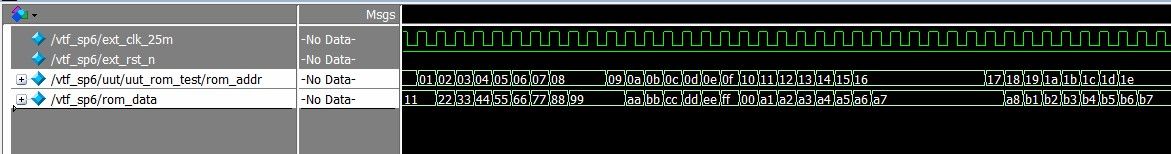

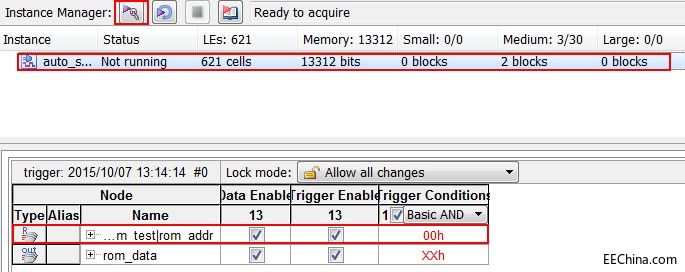

图9.32 ROM仿真波形2 图9.33 ROM仿真波形3 这里需要注意,rom_addr出现新地址时,rom_data对应的数据要延时一个时钟周期才会出现。以最后一个图为例,当rom_addr = 0x01时,rom_data对应的数据时0x22,比地址出现晚一个时钟周期。 连接好下载线,给CY4开发板供电。点击菜单“Tools à SignalTap II Logic Analyzer”,进入逻辑分析仪主页面。在右侧的“JTAG China Configuration”窗口中,建立好USB Blaster的连接后,点击“SOF Manager”后面的Programmer按钮进行下载。 如图9.34所示,在“trigger”下面罗列了我们已经添加好的需要观察的信号,尤其是在rom_addr信号的TriggerConditions一列,我们设置了值00h,表示rom_addr的值为0时我们将触发采集。另外,我们用鼠标点击选中Instance下面的唯一一个选项,然后单击InstanceManager后面的运行按钮,执行一次触发采集。

图9.33 ROM仿真波形3 这里需要注意,rom_addr出现新地址时,rom_data对应的数据要延时一个时钟周期才会出现。以最后一个图为例,当rom_addr = 0x01时,rom_data对应的数据时0x22,比地址出现晚一个时钟周期。 连接好下载线,给CY4开发板供电。点击菜单“Tools à SignalTap II Logic Analyzer”,进入逻辑分析仪主页面。在右侧的“JTAG China Configuration”窗口中,建立好USB Blaster的连接后,点击“SOF Manager”后面的Programmer按钮进行下载。 如图9.34所示,在“trigger”下面罗列了我们已经添加好的需要观察的信号,尤其是在rom_addr信号的TriggerConditions一列,我们设置了值00h,表示rom_addr的值为0时我们将触发采集。另外,我们用鼠标点击选中Instance下面的唯一一个选项,然后单击InstanceManager后面的运行按钮,执行一次触发采集。 图9.34 触发信号 波形如图9.35、图9.36所示。大家可以对照我们的ROM初始化文件rom_init.mif中对应每个地址的数据与我们这里采集的是否一致。当然了,大家必须注意,地址rom_addr所对应的数据会相应滞后2个时钟周期后出现。例如,地址01h的数据不是11h,而是22h,以此类推。

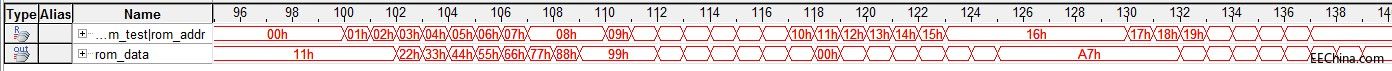

图9.34 触发信号 波形如图9.35、图9.36所示。大家可以对照我们的ROM初始化文件rom_init.mif中对应每个地址的数据与我们这里采集的是否一致。当然了,大家必须注意,地址rom_addr所对应的数据会相应滞后2个时钟周期后出现。例如,地址01h的数据不是11h,而是22h,以此类推。 图9.35 ROM实例在线逻辑分析仪采集波形1

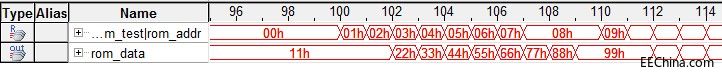

图9.35 ROM实例在线逻辑分析仪采集波形1 图9.36 ROM实例在线逻辑分析仪采集波形2

图9.36 ROM实例在线逻辑分析仪采集波形2