可调节输出低压差稳压器的降噪网

2018年06月13日 17:28 发布者:Ameya360

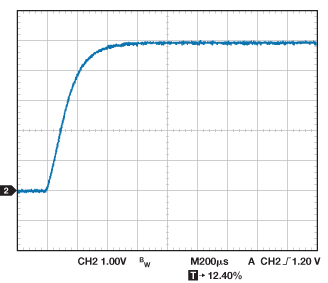

简介低压差稳压器(LDO)可用来为高速时钟、模数转换器、数模转换器、压控振荡器和锁相环这些电路供电。噪声对于高性能模拟电路的设计人员而言极为重要。降低噪声的关键是保持LDO噪声增益接近单位增益,且不影响交流性能或直流闭环增益。本文描述简单的RC网络如何降低可调节输出低压差稳压器的输出噪声。本文通过实验数据来演示这一简单方法的有效性。虽然RC网络的主要目的是降噪,但它也能改善电源抑制和负载瞬态响应。图 1 显示典型可调节输出LDO的简化框图。输出电压VOUT等于基准电压与误差放大器直流闭环增益的乘积:VOUT = VR × (1 + R1/R2),其中(1 + R1/R2)是误差放大器的直流闭环增益。误差放大器噪声VN和基准电压噪声VRN放大相同的倍数,使输出噪声与设定的输出电压成比例增加。这使得输出电压上的噪声比参考电压高但小于 2 倍,输出噪声适度增加但在敏感应用 中哪怕这种适度增加都有可能无法接受。(b) 使用降噪网络图 6. 可调节输出 LDO ADP125 的瞬态负载响应对启动时间的影响降噪网络的一个缺点是它会极大地增加启动时间。图 7 显示使用与不使用降噪网络时的ADP125 启动时间。正常启动时间约为 600 μs。若C1 = 10 nF,则启动时间增至 6 ms;若C1 = 1 μF,则增至 600 ms。对于电路完全上电后不再开关LDO的应用而言,启动时间增加应该不是问题。

(a) 不使用降噪网络

)

(c) 使用降噪网络,C1 = 1 μF图 7. 可调节输出 LDO ADP125 的启动时间结论通过添加一个简单的RC降噪网络,便可明显改善可调节输出LDO的噪声、电源抑制和瞬态性能,为高速时钟、模数转换器、数模转换器、压控振荡器和锁相环等噪声敏感型应用带来极大的优势。ADP125, ADP171, ADP1741, ADP1753, ADP1755, ADP7102, ADP7104, 和 ADP7105等LDO均具有这种通用架构,并将极大 地受益于降噪网络的使用。该技巧可用于与图 2 所示相似的 LDO架构,在该架构中,基准电压噪声和误差放大器噪声均由 直流闭环增益放大,因此输出噪声与输出电压成比例关系。较新的超低噪声LDO――比如ADM7151不会得益于此降 噪网络,因为该架构采用单位增益LDO误差放大器,所以基准电压等于输出电压。此外,内部基准电压滤波器极点低于 1 Hz,可极大地过滤基准电压,并消除几乎全部基准电压噪声影响。来源:网络,如侵删