勇敢的芯伴你玩转Altera FPGA连载38::Verilog代码风格之双向管脚的控制代码

2018年01月08日 21:03 发布者:rousong1989

勇敢的芯伴你玩转Altera FPGA连载38::Verilog代码风格之双向管脚的控制代码特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 对于单向的管脚,输入信号或者输出信号,他们的控制比较简单,不需要太复杂的控制,输入信号可以直接用在各类等式的右边用于作为赋值的一个因子;而输出信号则通常在等式的左边被赋值。那么,既可以作为输入信号又可以作为输出信号的双向信号又是如何进行控制的呢?如果直接的和单向控制一样即做输入又做输出,势必会使信号的赋值发生紊乱。列举一个简单的冲突,就是当输入0而输出1时到底这个信号是什么值?而我们如何控制才能够避免这类我们不期望的赋值情况发生?我们可以先看看表5.1所列出的I/O驱动真值表。表5.1 I/O驱动真值表

对于单向的管脚,输入信号或者输出信号,他们的控制比较简单,不需要太复杂的控制,输入信号可以直接用在各类等式的右边用于作为赋值的一个因子;而输出信号则通常在等式的左边被赋值。那么,既可以作为输入信号又可以作为输出信号的双向信号又是如何进行控制的呢?如果直接的和单向控制一样即做输入又做输出,势必会使信号的赋值发生紊乱。列举一个简单的冲突,就是当输入0而输出1时到底这个信号是什么值?而我们如何控制才能够避免这类我们不期望的赋值情况发生?我们可以先看看表5.1所列出的I/O驱动真值表。表5.1 I/O驱动真值表驱动源 0 1 x Z

0 0 X X 0

1 X 1 X 1

X X X X X

Z 0 1 X Z

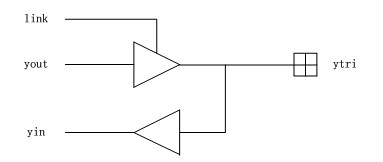

在这个表里,我们发现当高祖态Z和0或1值同时出现时,总能保持0或1的原状态不变。我们在设计双向管脚的逻辑时正要利用这个特性,管脚在做输入时,让输出值取Z状态,那么读取的输入值就完全取决于实际的输入管脚状态,而与输出值无关;管脚在做输出时,则只要保证与器件管脚连接的信号也是处于类似的Z状态便可以正常输出我们的信号值。当然了,外部的状态是用对应芯片或外设的时序来保证的,我们在FPGA器件内部不直接可控,但我们还是可以把握好FPGA内部的输入、输出状态,保证不出现冲突情况。 费了不少口舌,我想其实只要一个图加几段代码,大家可能就明白其中的精髓。如图5.9所示,link信号的高低用于控制双向信号的值是输出信号yout还是高阻态Z,当link控制当前的输出状态为Z时,则输入信号yin的值由管脚信号ytri来决定。

图5.9 双向信号控制 实现代码如下:// Verilog例程module bidir(ytri,…);inout ytri;… reg link;wire yin; … // link的取值控制逻辑以及其他逻辑 assign ytri = link ?yout:1'bz; assign yin = ytri; … // yin用于内部赋值 endmodule

图5.9 双向信号控制 实现代码如下:// Verilog例程module bidir(ytri,…);inout ytri;… reg link;wire yin; … // link的取值控制逻辑以及其他逻辑 assign ytri = link ?yout:1'bz; assign yin = ytri; … // yin用于内部赋值 endmodule