例说FPGA连载62:电子点菜单之FIFO例化说明

2016年12月26日 16:48 发布者:rousong1989

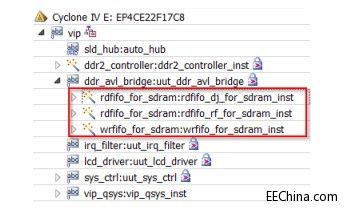

例说FPGA连载62:电子点菜单之FIFO例化说明特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc ddr_avl_bridge.v模块中,使用了3个FIFO,分别用于DDR2数据写入缓存和DDR2数据读出缓存。如图10.6所示,实际上,我们只需要例化两种类型的FIFO,即图示的名称为rdfifo_for_sdram和wrfifo_for_sdram的两个FIFO。

ddr_avl_bridge.v模块中,使用了3个FIFO,分别用于DDR2数据写入缓存和DDR2数据读出缓存。如图10.6所示,实际上,我们只需要例化两种类型的FIFO,即图示的名称为rdfifo_for_sdram和wrfifo_for_sdram的两个FIFO。 图10.6 FIFO模块截图 为什么这里可以有两个名称为“rdfifo_for_sdram”的FIFO呢?其实,仔细看,你会发现这两个FIFO在“:”后面的名称不一样。一个为“rdfifo_dj_for_sdram_inst”,另一个为“rdfifo_rf_for_sdram_inst”。我们可以先到ddr_avl_bridge.v模块的verilog代码中查看一下这两个FIFO的例化。//例化SDRAM读出数据缓存FIFO模块rdfifo_for_sdram rdfifo_rf_for_sdram_inst( .aclr(!local_rst_n || rdfifo_clr_r), .data(local_rdata), //128bit input .rdclk(clk_33m), .rdreq(lcd_rfreq), .wrclk(phy_clk), .wrreq(local_rdata_valid && rf_dj_flag), .q(lcd_rfdb), //16bit output .wrusedw(rfifo_rf_used) ); //例化SDRAM读出数据缓存FIFO模块rdfifo_for_sdram rdfifo_dj_for_sdram_inst( .aclr(!local_rst_n || rdfifo_clr_r), .data(local_rdata), //128bit input .rdclk(clk_33m), .rdreq(lcd_djreq), .wrclk(phy_clk), .wrreq(local_rdata_valid && !rf_dj_flag), .q(lcd_djdb), //16bit output .wrusedw(rfifo_dj_used) ); 我们在一开始讲解IP核例化的时候就提到过,如这里的“rdfifo_for_sdram”是我们配置的IP核名称,而“rdfifo_rf_for_sdram_inst”则是我们在应用中集成的模块名称。换句话说,同一个工程中,可以有多个不同名称的IP核模块(如“rdfifo_rf_for_sdram_inst”),它们的配置都是出于同一个IP核(如“rdfifo_for_sdram”)。或者,我们可以认为这类似与C语言中多次调用同一个函数,只不过,对于FPGA逻辑而言,每一次“调用”都必须实打实的消耗一份“资源”。

图10.6 FIFO模块截图 为什么这里可以有两个名称为“rdfifo_for_sdram”的FIFO呢?其实,仔细看,你会发现这两个FIFO在“:”后面的名称不一样。一个为“rdfifo_dj_for_sdram_inst”,另一个为“rdfifo_rf_for_sdram_inst”。我们可以先到ddr_avl_bridge.v模块的verilog代码中查看一下这两个FIFO的例化。//例化SDRAM读出数据缓存FIFO模块rdfifo_for_sdram rdfifo_rf_for_sdram_inst( .aclr(!local_rst_n || rdfifo_clr_r), .data(local_rdata), //128bit input .rdclk(clk_33m), .rdreq(lcd_rfreq), .wrclk(phy_clk), .wrreq(local_rdata_valid && rf_dj_flag), .q(lcd_rfdb), //16bit output .wrusedw(rfifo_rf_used) ); //例化SDRAM读出数据缓存FIFO模块rdfifo_for_sdram rdfifo_dj_for_sdram_inst( .aclr(!local_rst_n || rdfifo_clr_r), .data(local_rdata), //128bit input .rdclk(clk_33m), .rdreq(lcd_djreq), .wrclk(phy_clk), .wrreq(local_rdata_valid && !rf_dj_flag), .q(lcd_djdb), //16bit output .wrusedw(rfifo_dj_used) ); 我们在一开始讲解IP核例化的时候就提到过,如这里的“rdfifo_for_sdram”是我们配置的IP核名称,而“rdfifo_rf_for_sdram_inst”则是我们在应用中集成的模块名称。换句话说,同一个工程中,可以有多个不同名称的IP核模块(如“rdfifo_rf_for_sdram_inst”),它们的配置都是出于同一个IP核(如“rdfifo_for_sdram”)。或者,我们可以认为这类似与C语言中多次调用同一个函数,只不过,对于FPGA逻辑而言,每一次“调用”都必须实打实的消耗一份“资源”。