例说FPGA连载57:液晶驱动功能概述

2016年12月12日 17:29 发布者:rousong1989

例说FPGA连载57:液晶驱动功能概述特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 本实例基本是移植工程实例5,将vga_ctrl.v模块替换为lcd_ctrl.v模块,也即VGA显示器的驱动要更迭为LCD显示屏的驱动。我们所使用的LCD显示屏是一款7寸大小、800*480分辨率、数字接口驱动的液晶屏。与VGA显示驱动的时序相比,LCD显示驱动的时序大同小异。LCD输出的色彩信号是直接通过565的RGB并口数字信号(即5bit代表R色彩,6bit代表G色彩,5bit代表B色彩)传输的;VGA输出的色彩信号,最终虽然是3个分别代表RGB的0~0.7V模拟电平,但是由于FPGA不能直接输出模拟信号,所以它们通过一颗3路的高速ADC芯片ADV7123来实现电平转换,因此在我们的FPGA驱动实现中,起始输出的也是和LCD一样的565的RGB数字信号。VGA的同步信号是HSYNC和VSYNC,它们在每行或每场数据的空闲产生高脉冲来达到同步的目的;而我们所使用的LCD,其信号同步方式不仅可以使用和VGA类似的HSYNC和VSYNC信号,也可以使用DE信号来实现同步。当然了,无论是HSYNC/VSYNC同步方式,还是DE同步方式,对我们内部驱动时序的逻辑计数要求都是差不多的。如图8.1所示,DE和HSYNC/VSYNC摆在一起,它们的关系一目了然。DE脉冲有效(高电平)期间,表示当前的RGB数据是有效的,即显示在显示屏上的像素点色彩数据。

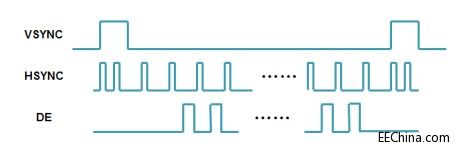

本实例基本是移植工程实例5,将vga_ctrl.v模块替换为lcd_ctrl.v模块,也即VGA显示器的驱动要更迭为LCD显示屏的驱动。我们所使用的LCD显示屏是一款7寸大小、800*480分辨率、数字接口驱动的液晶屏。与VGA显示驱动的时序相比,LCD显示驱动的时序大同小异。LCD输出的色彩信号是直接通过565的RGB并口数字信号(即5bit代表R色彩,6bit代表G色彩,5bit代表B色彩)传输的;VGA输出的色彩信号,最终虽然是3个分别代表RGB的0~0.7V模拟电平,但是由于FPGA不能直接输出模拟信号,所以它们通过一颗3路的高速ADC芯片ADV7123来实现电平转换,因此在我们的FPGA驱动实现中,起始输出的也是和LCD一样的565的RGB数字信号。VGA的同步信号是HSYNC和VSYNC,它们在每行或每场数据的空闲产生高脉冲来达到同步的目的;而我们所使用的LCD,其信号同步方式不仅可以使用和VGA类似的HSYNC和VSYNC信号,也可以使用DE信号来实现同步。当然了,无论是HSYNC/VSYNC同步方式,还是DE同步方式,对我们内部驱动时序的逻辑计数要求都是差不多的。如图8.1所示,DE和HSYNC/VSYNC摆在一起,它们的关系一目了然。DE脉冲有效(高电平)期间,表示当前的RGB数据是有效的,即显示在显示屏上的像素点色彩数据。 图8.1 基于HSY/VSY和DE的LCD驱动时序波形 相对于HSYNC/VSYNC驱动,DE驱动方式反而更简洁一些,它的时序波形如图8.2所示。

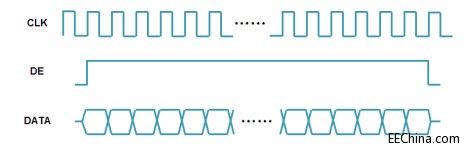

图8.1 基于HSY/VSY和DE的LCD驱动时序波形 相对于HSYNC/VSYNC驱动,DE驱动方式反而更简洁一些,它的时序波形如图8.2所示。 图8.2 基于DE的LCD驱动时序波形 为了便于实际的驱动计数器的时序产生,我们还是需要和HSYNC/VSYNC驱动方式一样,对行和列计数器的同步脉冲、后沿脉冲、显示脉冲、前沿脉冲做定义,它的脉冲计数参数如表8.1所示。注意列的单位为“行”,而行的单位为“基准时钟周期数”,即33MHz时钟脉冲数。表8.1 LCD驱动时序参数表

图8.2 基于DE的LCD驱动时序波形 为了便于实际的驱动计数器的时序产生,我们还是需要和HSYNC/VSYNC驱动方式一样,对行和列计数器的同步脉冲、后沿脉冲、显示脉冲、前沿脉冲做定义,它的脉冲计数参数如表8.1所示。注意列的单位为“行”,而行的单位为“基准时钟周期数”,即33MHz时钟脉冲数。表8.1 LCD驱动时序参数表行/列同步脉冲后沿脉冲显示脉冲前沿脉冲帧长

列02348022525

行0468002101056

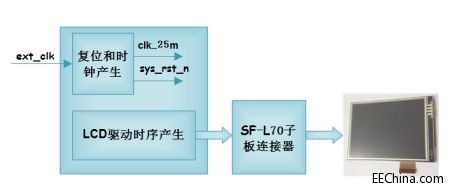

本实例连接VIP1核心板和SF-L70子板进行实验。通过移植工程实例5的驱动代码,可以产生7寸800*480液晶屏的驱动时序。该实例的功能框图如图8.3所示。

图8.3工程实例6功能框图

图8.3工程实例6功能框图