逻辑分析仪我也DIY(四)―神秘蓝点

2016年02月19日 09:05 发布者:designapp

今晚把各个显示的字符都DIY上去了,不过在某些蓝色字符附近出现了许多意外的神秘蓝点,如下:

上面一共四个Ch字符中,只有Ch2是完全没有问题的,特权同学就感觉很纳闷了,为什么同样的16个Ch字符,就这几个出现这些神秘的蓝点。家中的LCD专家还特地给分析了,这个Cha前面的点那是四个像素的蓝点在一起,觉得不是坏点,那一定是认为打上去的。换我的话说,那是FPGA给送上去的点。所以回头来显示走读代码找问题,一通找,最后还是没发现什么不对的地方。因为时序约束后还都有较大的余量,所以这个原因排除,而这个字模是存储在M4K配置的ROM里的,所以问题很可能和它有关系,ROM的配置后又一个可选的输出数据是否要让输入时钟打一拍,默认是打一拍,我一直以为这里的打一拍不打一拍问题不是很大,不打一拍,送完地址的第二个时钟周期出数据,而打一拍应该是送完地址的第三个时钟周期出数据,所以也没太在意。

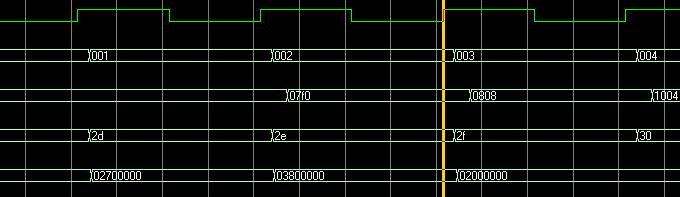

无奈之下只能重新让ModelSim里帮忙找问题,再次进行后仿真,这次就抓住出问题的地方,本想找扫描到的点位置送出来的数据是否正确。结果由于这个时间也太长了,咱等不起,索性就认真的就ROM的时序做起了文章,这一看可不要紧,问题浮出水面。

第1条是ROM的输入时钟;

第2条是ROM1的地址(输出数据没有用时钟打一拍);

第3条是ROM1的输出数据;

第4条是ROM2的地址(输出数据打了一拍);

第5条是ROM2的输出数据。

ROM1里,地址001的数据是0710,地址002的数据是0808;ROM2里地址2d的数据是02000000。我想问题就出来了,对于ROM1在第一个时钟上升沿送完地址后(延时一点到达),第二个时钟上升沿虽然数据出现了,但是我们的时钟是采不到的,它是在第二个时钟上升沿的建立保持时间后才出现在总线上的,所以真正意思上读出数据的时间应该是时钟的第三个上升沿。ROM2也类似,由于内部时钟打了一拍,所以它比ROM1要再慢一个时钟周期。这就是我的问题所在,换句话说,字模数据显示位置整个右移了一个坐标。

随后,地址再早一个时钟周期置位,问题解决了。

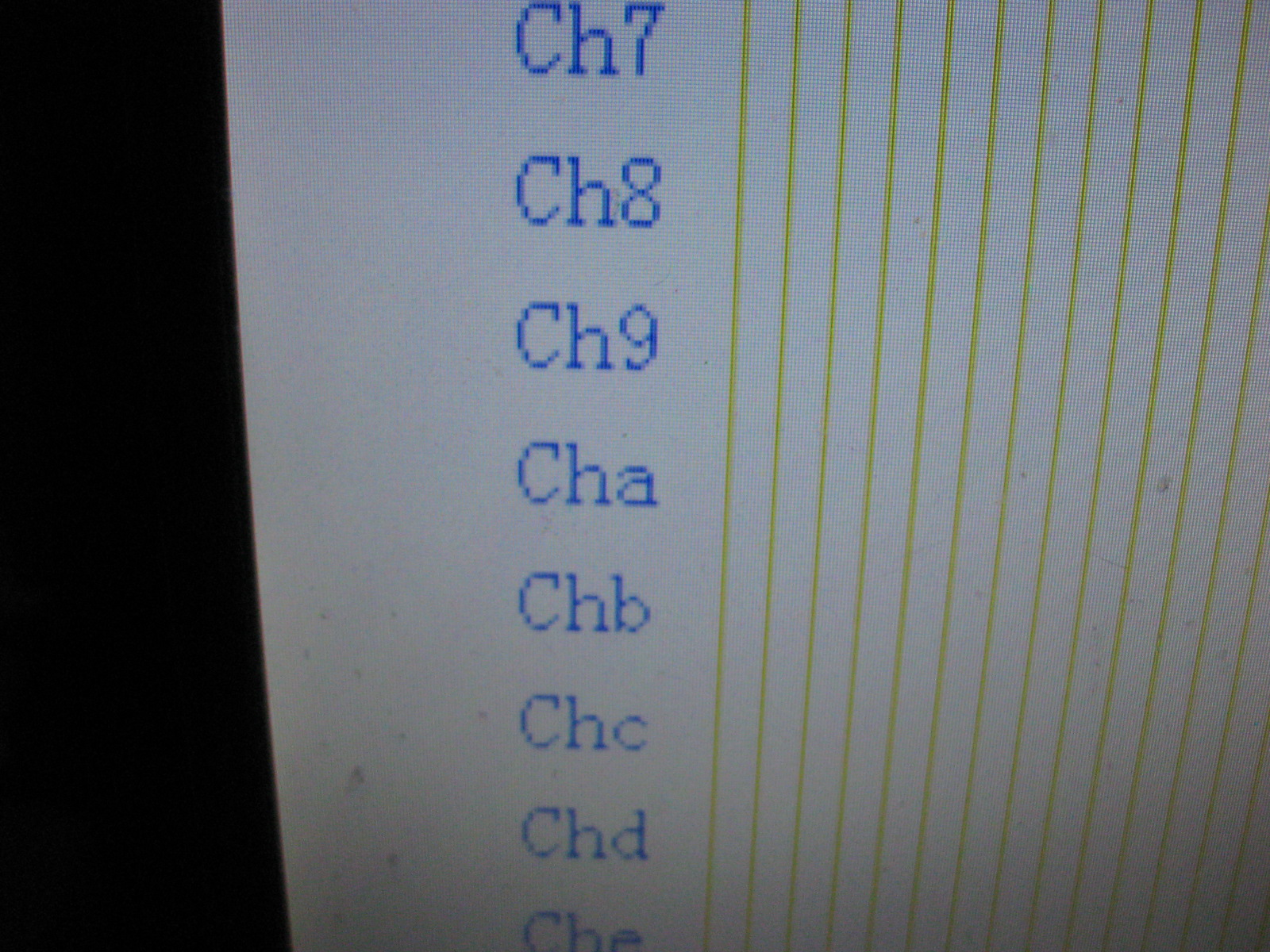

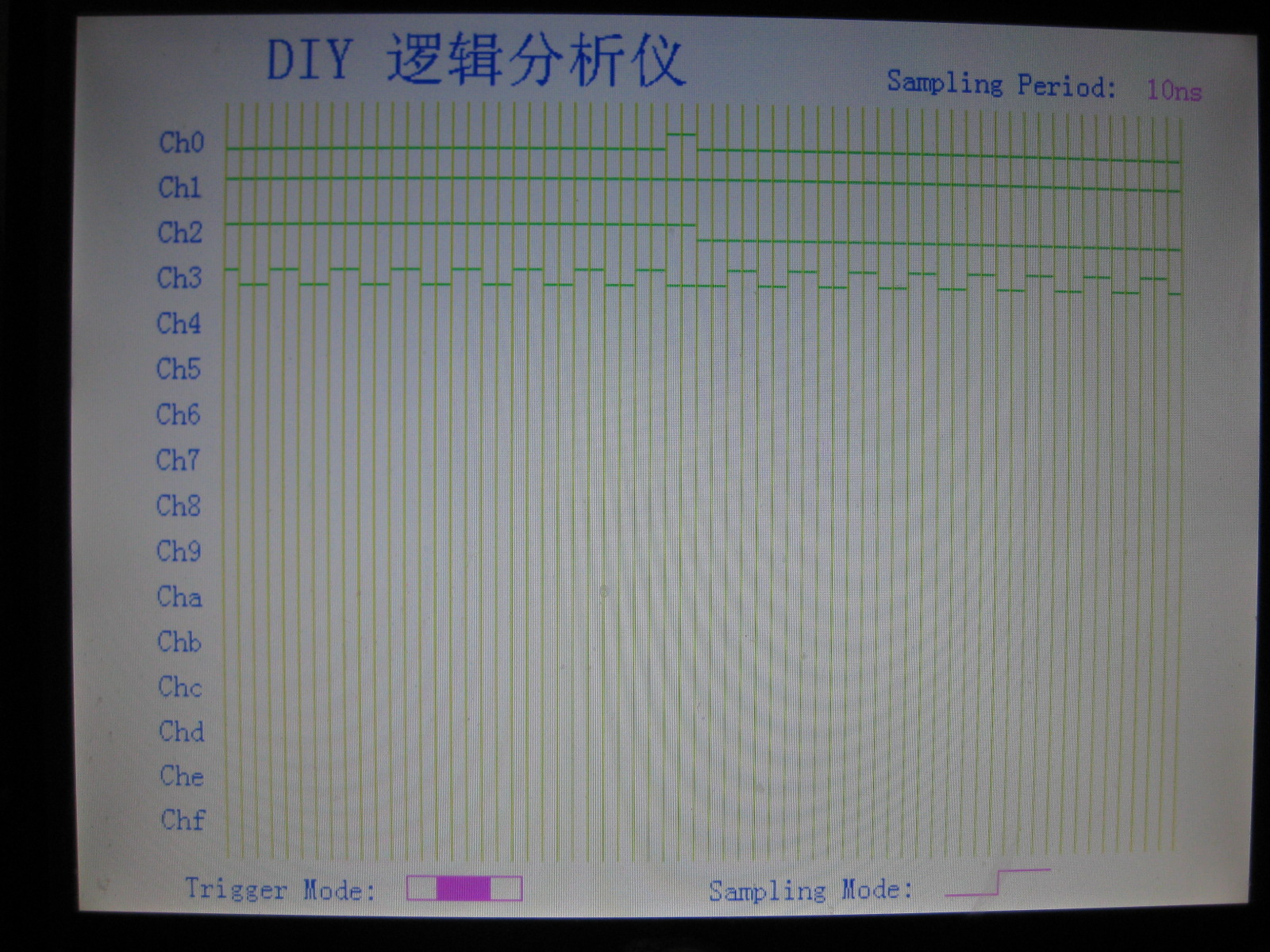

今晚过后,整个就下面的一个效果。

采样模式显示。

采样周期可调,从10ns到100us可调。

三种采样模式显示。