FPGA实战演练逻辑篇31:超声波与视频采集子板设计概述

2015年06月01日 12:00 发布者:rousong1989

超声波与视频采集子板设计概述本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt SF-SENSOR子板主要外设芯片及其功能描述如表3.10。(特权同学,版权所有)表3.10 SF-SENSOR子板主要外设与功能描述外设芯片 主要功能

32PIN的OUPLLN插座P1 用于SF-SENSOR子板上的各个外设与SF-CY3核心板相连。

16PIN的插座P2 用于连接视频采集模块。

4PIN的插座P4 用于连接超声波模块。

2PIN的插座P3 焊接RTC电池座,安装纽扣电池后,用于给RTC芯片供电。

芯片PCF8563T(U2) NXP的实时时钟(RTC)芯片。

芯片GT21L16S2W(U1) 集通公司的中文字库芯片。

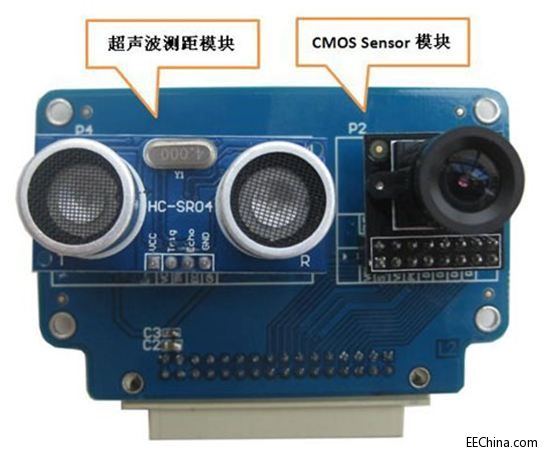

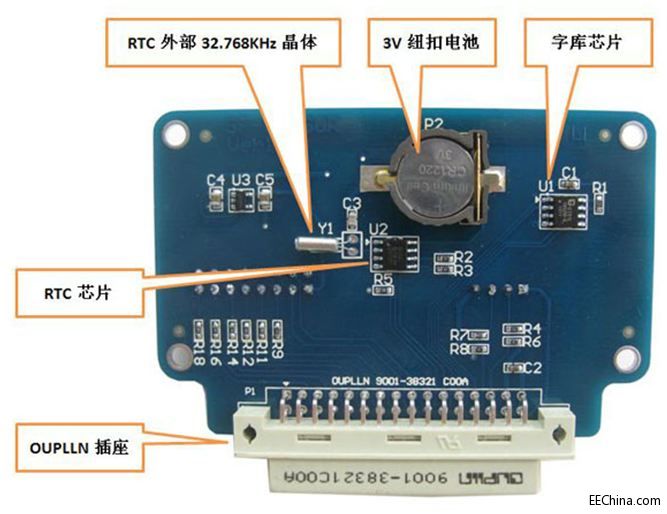

SF-SENSOR子板主要外设芯片的实物位置如图3.72和图3.73所示。(特权同学,版权所有)

图3.72SF-SENSOR子板实物照片1

图3.72SF-SENSOR子板实物照片1 图3.73SF-SENSOR子板实物照片2 SF-SENSOR子板的P1插座定义如图3.78所示,。(特权同学,版权所有)

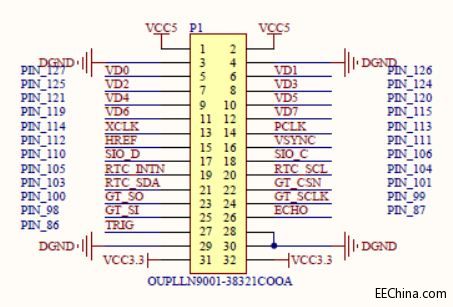

图3.73SF-SENSOR子板实物照片2 SF-SENSOR子板的P1插座定义如图3.78所示,。(特权同学,版权所有) 图3.78SF-SENSOR子板与FPGA的连接插座电路SF-SENSOR与FPGA引脚定义如表3.15所示。(特权同学,版权所有)表3.15SF-SENSOR与FPGA引脚定义

图3.78SF-SENSOR子板与FPGA的连接插座电路SF-SENSOR与FPGA引脚定义如表3.15所示。(特权同学,版权所有)表3.15SF-SENSOR与FPGA引脚定义分类 名称 引脚号 功能描述

视频接口 SIO_C 106 用于配置CMOS Sensor芯片内部寄存器的I2C接口时钟信号。

SIO_D 110 用于配置CMOS Sensor芯片内部寄存器的I2C接口数据信号。

VSYNC 111 伴随视频数据输出的场同步信号。

HREF 112 伴随视频数据输出的行同步信号。

PCLK 113 用于视频数据总线同步的时钟信号。

XCLK 114 外部(FPGA)输给CMOS Sensor芯片工作的时钟信号。

VD7 115 CMOS Sensor输出的视频数据总线。

VD6 119 CMOS Sensor输出的视频数据总线。

VD5 120 CMOS Sensor输出的视频数据总线。

VD4 121 CMOS Sensor输出的视频数据总线。

VD3 124 CMOS Sensor输出的视频数据总线。

VD2 125 CMOS Sensor输出的视频数据总线。

VD1 126 CMOS Sensor输出的视频数据总线。

VD0 127 CMOS Sensor输出的视频数据总线。

超声波接口 TRIG 86 超声波模块的触发输入信号。

ECHO 87 超声波模块的响应输出信号。

RTC接口 RTC_SDA 103 用于读写寄存器的I2C总线数据信号。

RTC_SCL 104 用于读写寄存器的I2C总线时钟信号。

RTC_INTN 105 RTC芯片中断产生引脚。

字库芯片接口 GT_CSN 101 SPI总线的片选信号,低电平有效。

GT_SCLK 99 SPI总线的时钟信号。

GT_SO 100 SPI总线的MISO信号,即主机(FPGA)输出从机(U1芯片)输入信号。

GT_SI 98 SPI总线的MOSI信号,即主机(FPGA)输入从机(U1芯片)输出信号。

SF-SENSOR子板与SF-CY3核心模块互联的是P1插座,该插座连接到SF-CY3的P2插座上,其实物连接如图3.79所示。(特权同学,版权所有)

图3.79SF-SENSOR子板与SF-CY3核心板的实物连接

图3.79SF-SENSOR子板与SF-CY3核心板的实物连接