FPGA实战演练逻辑篇30:FT232之UART电路设计

2015年05月29日 10:17 发布者:rousong1989

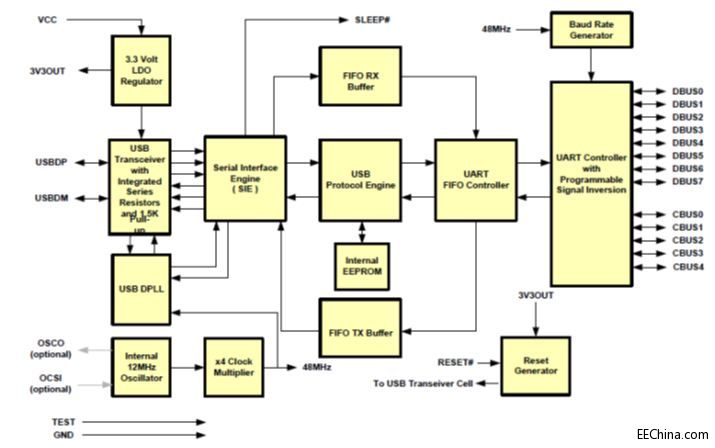

FT232之UART电路设计本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt FT232芯片内部功能框图如图6.68所示。它通过USB的D+/D-与PC进行通信,芯片内部能够根据USB协议对数据进行处理,最终通过FIFO将这些数据转换为UART协议和我们的FPGA进行通信。(特权同学,版权所有) 图6.68 FT232芯片内部功能框图 FT232R的接口电路如图6.69所示。P4为USB port,用于连接PC,UART_TX和UART_RX分别为FT232R芯片的UART发送和UART接收信号,对应的,UART_TX就是FPGA的UART接收,而UART_RX就是FPGA的UART发送信号。D2和D3连接着U2-23/22,在UART_RX和UART_TX收发的时候它们会闪烁以指示工作状态。(特权同学,版权所有)

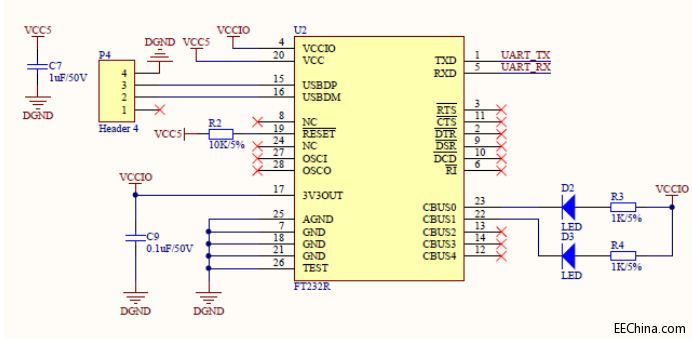

图6.68 FT232芯片内部功能框图 FT232R的接口电路如图6.69所示。P4为USB port,用于连接PC,UART_TX和UART_RX分别为FT232R芯片的UART发送和UART接收信号,对应的,UART_TX就是FPGA的UART接收,而UART_RX就是FPGA的UART发送信号。D2和D3连接着U2-23/22,在UART_RX和UART_TX收发的时候它们会闪烁以指示工作状态。(特权同学,版权所有) 图6.69 FT232接口电路 FT232R的引脚定义如表3.8所示。(特权同学,版权所有)表3.8 FT232引脚定义

图6.69 FT232接口电路 FT232R的引脚定义如表3.8所示。(特权同学,版权所有)表3.8 FT232引脚定义引脚号 引脚名称 类型 说明

15 USBDP I/O USB差分信号正,内部集成串联电阻和1.5K ohm上拉到3.3V。

16 USBDM I/O USB差分信号负,内部集成串联电阻。

4 VCCIO PWR I/O供电电压。

7,18,21 GND PWR 芯片的地引脚。

17 3V3OUT O 经过内部LDO输出的3.3V电压,最大供电电流50mA。

20 VCC PWR 芯片核电压,可以供3.3V~5.25V。

25 AGND PWR 用于内部时钟倍频的模拟地。

8,24 NC NC 无连接。

19 RESET# I 复位引脚,低电平有效。内部有上拉电阻,不使用该引脚可以浮空。

26 TEST I 内部测试引脚,正常工作是必须接地。

27 OSCI I 12MHz晶体输入引脚。

28 OSCO O 12MHz晶体输出引脚。

1 TXD O 芯片的UART数据发送信号。

2 DRT# O 数据终端准备控制输出/握手信号。

3 RTS# O 请求发送控制输出/握手信号。

5 RXD I 芯片的UART数据接收信号。

6 RI# I 振铃提示控制输入信号。

9 DSR# I 数据设置准备控制输入/握手信号。

10 DCD# I 数据传输检测控制输入。

11 CTS# I 清除发送控制输入/握手信号。

12 CBUS4 I/O 可配置CBUS输出引脚。

13 CBUS2 I/O 可配置CBUS输出引脚。

14 CBUS3 I/O 可配置CBUS输出引脚。

22 CBUS1 I/O 可配置CBUS输出引脚。

23 CBUS0 I/O 可配置CBUS输出引脚。