FPGA实战演练逻辑篇29:CH376之USB电路设计

2015年05月24日 19:57 发布者:rousong1989

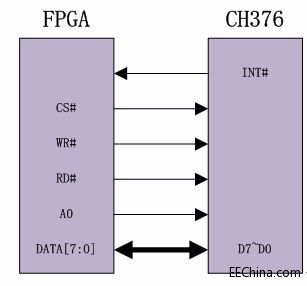

CH376之USB电路设计本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt CH376S是文件管理控制芯片,用于单片机/DSP/MCU/MPU系统读写U盘或者SD卡中的文件。CH376S支持USB设备方式和USB 主机方式,并且内置了USB通讯协议的基本固件,内置了处理海量存储设备的专用通讯协议的固件,内置了SD卡的通讯接口固件,内置了FAT12、FAT16和FAT32文件系统的管理固件,支持常用的USB存储设备(包括U 盘/USB硬盘/USB闪存盘/USB读卡器)和SD卡(包括标准容量SD卡和高容量HC-SD卡以及协议兼容的MMC卡和TF卡)。(特权同学,版权所有)CH376S支持三种通讯接口:8位并口(SF-USB子板的硬件接口方式)、SPI接口或者异步串口。单片机/DSP/MCU/MPU等控制器可以通过上述任何一种通讯接口控制CH376S芯片,从而存取U盘、SD卡中的文件或者与PC通信。(特权同学,版权所有) FPGA与CH376S之间通过一组并口总线进行通信。如图3.65所示,FPGA处于主机(注意这里所说的主机和从机只是针对并口通信而言,不是指USB的主机和从机)地位,它通过片选信号CS#、写选通信号WR#、读选通信号RD#、指令\数据信号A0和数据总线DATA对CH376S的数据或控制寄存器进行读写。CH376S处于从机地位,当它需要返回数据时,则通过中断信号INT#向FPGA发出请求,然后FPGA根据当前发送过的指令状态执行相应的读取或写入操作。(特权同学,版权所有) 图3.65 FPGA与CH376S互联 CH376S的接口电路图如图3.66所示,其SD卡接口的电路如图3.67所示。P3为USB port,X1为12MHz的晶体,P2为SD座。(特权同学,版权所有)

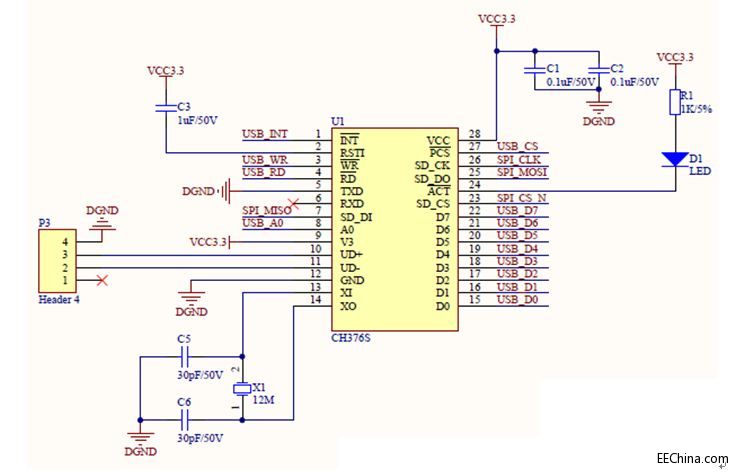

图3.65 FPGA与CH376S互联 CH376S的接口电路图如图3.66所示,其SD卡接口的电路如图3.67所示。P3为USB port,X1为12MHz的晶体,P2为SD座。(特权同学,版权所有) 图3.66 CH376S接口电路

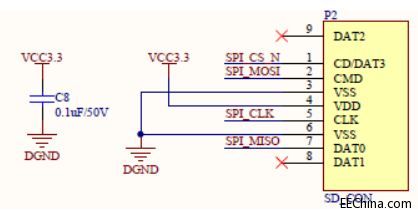

图3.66 CH376S接口电路 图3.67 SD卡接口电路 CH376S的引脚定义如表3.7所示。(特权同学,版权所有)表3.7 CH376S引脚定义

图3.67 SD卡接口电路 CH376S的引脚定义如表3.7所示。(特权同学,版权所有)表3.7 CH376S引脚定义引脚号 引脚名称 类型 说明

28 VCC 电源 正电源输入端,需要外接0.1uF退偶电容。

12 GND 电源 公共接地端,需要连接USB总线的地线。

9 V3 电源 3.3V电源时,连接VCC输入外部电源;5V电源时,外接0.01uF退偶电容。

13 X1 输入 晶体振荡的输入端,需要外接12MHz晶体。

14 X0 输入 晶体振荡的反向输入端,需要外接12MHz晶体。

10 UD+ USB信号 USB总线的U+数据。

11 UD- USB信号 USB总线的U-数据。

23 SD_CS 开漏输出 SD卡SPI接口的片选输出,低电平有效,内置上拉电阻。

26 SD_CK 输出 SD卡SPI接口的串行时钟输出。

7 SD_DI 输入 SD卡SPI接口的串行输入数据,内置上拉电阻。

25 SD_DO 输出 复用引脚;SD卡SPI接口的串行数据输出。

25 RST 输出 复用引脚;在进入SD卡模式之前是电源上电复位和外部复位输出,高电平有效。

22~15 D0~D7 双向三态 并口的8位双向数据总线,内置上拉电阻。

18 SCS 输入 SPI接口的片选输入,低电平有效,内置上拉电阻。

20 SCK 输入 SPI接口的串行时钟输入,内置上拉电阻。

21 SDI 输入 SPI接口的串行数据输入,内置上拉电阻。

22 SDO 三态输出 SPI接口的串行数据输出。

19 BZ 输出 SPI接口的忙状态输出,高电平有效。

8 A0 输入 并口的地址输入,区分命令和数据;内置上拉电阻,当A0=1时可以而写命令或读状态,当A0=0时可以读写数据。

27 PCS# 输入 并口的片选输入,低电平有效,内置上拉电阻。

4 RD# 输入 并口的读选通输入,低电平有效,内置上拉电阻。

3 WR# 输入 并口的写选通输入,低电平有效,内置上拉电阻。

5 TXD 输入 /输出 在芯片内部复位期间为接口配置输入,内置上拉电阻; 在芯片复位完成后为异步串口的串行数据输出。

6 RXD 输入 异步串口的串行数据输入,内置上拉电阻。

1 INT# 输出 中断请求输出,低电平有效,内置上拉电阻。

24 ACT# 开漏输出 状态输出,低电平有效,内置上拉电阻。在USB主机方式下是USB设备正在连接状态输出;在SD卡主机方式下是SD卡SPI通讯成功状态输出;在内置固件的USB设备方式下是USB设备配置完成状态输出。

2 RSTI 输入 外部复位输出,高电平有效,内置下拉电阻。

网友评论

spy007868 2015年07月22日

谢谢分享

谢谢分享

不错