一种新型无运放CMOS带隙基准电路

2015年03月10日 11:03 发布者:designapp

1 引言几乎所有的模拟电路都需要稳定的电压源。电压源的温度系数。抗噪声能力直接影响着电路的性能与精度。带隙基准因为较低的温度系数,与电源和工艺的相对无关性,与CMOS工艺较好的兼容性等,得到了广泛应用。

首先阐述了带隙基准的基本原理,然后介绍了常规的带隙基准结构。在此基础上,提出了一种新型带隙基准电路。该电路结构简单,具有较低的温度系数和较高的电源抑制比。

2 带隙基准的基本原理

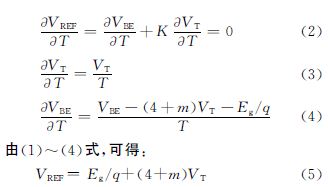

带隙基准产生基准电压源,如(1)式所示,是利用双极晶体管基极-发射极电压VBE得到的具有负温度系数的电压和利用热电势VT得到的正温度系数电压的倍数相加,得到与温度无关的基准电压源。热电势VT的关系式通常用两个相同晶体管的VBE差值产生。

VREF = VBE+KVT (1)

(1)式两边分别对温度求导,并将温度系数置零,得到:

当VT为零时,VREF 等于硅的带隙电压Eg/q,故称为带隙基准电压。

3 电路结构及其分析

3.1 常规的带隙基准电路

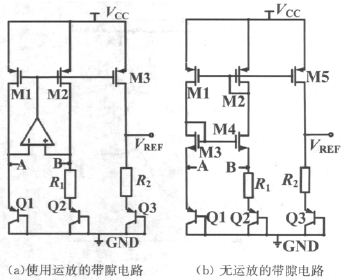

图1所示是两种常规的带隙基准电路,两者都是通过箝制A,B点电压相等,产生PTAT电流,再通过电阻R2将该电流转变为电压,与晶体管的VEB相加,得到基准电压。两者不同点是图1(a)所示电路使用运算放大器,图1(b)所示电路使用电流镜,使A,B电压相等。运放带隙基准的性能受运算放大器的失调电压。电源抑制比。增益等的严重影响。虽然可以通过仔细设计运算放大器得到很好的性能,但是运算放大器不仅引入了新的噪声和功耗,而且还增加了设计难度。电流镜带隙基准电路虽然没有使用运算放大器,但是因为沟道调制效应等原因,也会造成基准源精度的降低。

图1 两种常规的带隙基准电路

本文在图1(b)常规 电流镜带隙基准电路的基础上,提出一种新型带隙基准电路,如图2所示。

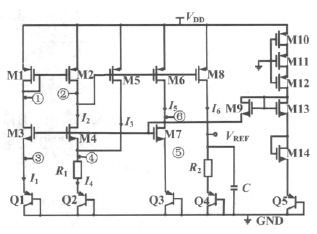

图2 新型带隙基准电压源

3.2 启动电路

因为带隙电路中存在简并偏置点,当电源上电时,有可能出现所有支路都传输零电流的情况,使整个电路不能正常工作。因此,需要启动电路让电路在上电时摆脱简并偏置点。

图2电路中的M9~M14和Q5组成启动电路。刚接通电源时,节点⑥为低电平。M9导通,给节点⑥充电。当节点⑥电压升到一定高度时,整个带隙基准电路开始正常工作,同时导致(6)式成立,从而在电路正常工作时M9处于截止状态。启动电路不再对电路产生影响,完成电路的启动。

VGS9=VCC-V⑥-VDS10-VDS11-VDS12=VCC-VEB3-VGS7-VDS10-VDS11-VDS12<VTH9 (6)

3.3 基准电压产生电路

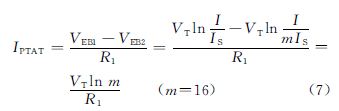

图2中,M1,M2,M5,M6宽长比的比例为2∶1∶1∶2。M3,M4,M7 宽长比的比例为2∶1∶2。Q1,Q3~Q5是一样的三极管,Q2是与Q1一样的16个三极管的并联。

M1~M5,Q1,Q2形成PTAT电流产生电路。M5还起反馈作用。M6,M7,Q3支路为M3,M4提供偏置电压,同时起负反馈作用,使节点①电压等于节点②电压。Q1和Q3是一样的三极管,M7和M3的栅极相连,使V⑤ =V③。假设节点③电压不等于节点⑤电压,如果V⑤>V③,由VBE1<VBE3得到I1<I5,而由VGS3>VGS7得到I1>I5,与前面得到的结论相矛盾,所以,V⑤=V③,I1=I5,VGS1=VGS6,从而得到节点①电压等于节点②电压。由电流镜和各个晶体管的尺寸比值,可得出IPTAT=I1=I2+I3=I4=I5=I6。因为M3和M4传输同样的电流,漏极电压又相等,它们接在同一个栅极电压上,所以,V④=V③。

(7)式得到的正温度系数电流IPTAT被镜像到M8,Q4,R2支路。通过该电流流过R2产生的电压和VEB4相加,得到所要的带隙基准电压。

由VEB和VT在室温下的温度系数,可得到零温度系数的基准:

VREF≈VEB+17.2 VT≈1.25(V) (10)

要使(10)式成立,两电阻关系需满足:

R2/R1=17.2/ln m (11)

但是,实际电路会与这个比值有所偏差。最终电路得到了约1.25V的基准电压。

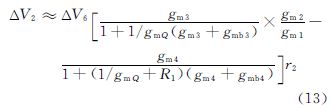

下面分析电路中两个支路的反馈作用。首先分析M6,M7所在反馈支路。假设节点2电压升高ΔV ,节点6电压变化为:

ΔV6= -gm6r6ΔV (12)

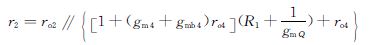

式中,r6为从节点6看进去的电阻:

ΔV 在M6,M7反馈支路经过环路一圈后,最终返回到节点2的电压变化量为:

式中,gmQ为三极管的跨导。从节点2看进去的电阻为:

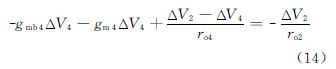

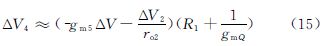

在M5反馈支路中,当节点2电压升高ΔV 时,可列出小信号方程:

节点4的电压变化量为:

由(14),(15)式得, ΔV 经过M5支路反馈后返回到节点2的电压变化量为:

从(13)和(16)式可 以看出,这两个支路反馈回来的电压量ΔV2均与-ΔV 成正比,所以是负反馈。这两路负反馈使电路比普通结构有更大的环路增益,从而提高了环路的抗干扰能力和电路的电源抑制比,减小了常规结构中沟道调制效应对基准源精度的影响。

4 仿真结果分析及电路版图设计

基于0.18μm的标准CMOS工艺库,对电路的启动过程。温度系数和电源抑制比进行仿真。

当电源电压从0~2.5V变化时,进行直流和瞬态仿真,检查电路能否启动。如图3所示,该电路能够正常启动。当电源电压为2.5V 时,在-40℃~125℃温度范围内观察基准电压VREF的变化。

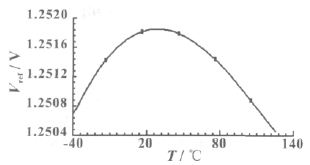

如图4所示,在室温(25℃)下,VREF的温度系数约为零。由图4曲线计算可得,该电路在这个温度范围内的温度系数为6.73×10-6 /℃。

图3 电路的启动仿真

ref的温度变化曲线">

图4 带隙基准输出电压Vref的温度变化曲线

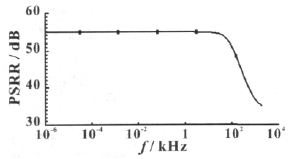

图5所示为电路的电源抑制比与频率的曲线。可见,该电路在低频时电源抑制比为54.8dB,具有较高的电源抑制比。在高电源电压下,可以应用共源共栅电路进一步增加电源抑制比。

图5 带隙基准的PSRR特性

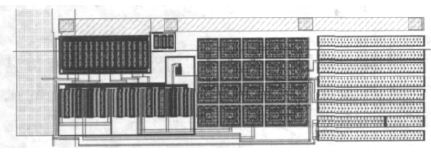

设计的带隙基准电路用于流水线A/D转换器。图6所示为电路版图。因为三极管Q1和Q2的匹配对电路精度影响很大,所以,在绘制版图时,让Q2包围Q1,以增加其匹配度。因为电阻值的绝对误差很大,而相对误差很小,所以,该电路版图的电阻按比例绘制,以减少误差。

图6 带隙基准电路版图

5 结论

本文设计了一种无运放带隙基准电路。该电路比传统运放带隙基准具有更少的功耗和噪声,并消除了运放失调电压等参数对基准精度的影响,减小了设计难度。该电路也比传统的无运放电流镜带隙基准具有更高的电压精度和电源抑制比。在2.5V电源电压下,在-40℃~125℃温度范围内,温度系数约为6.7×10-6/℃,电源抑制比为55dB。