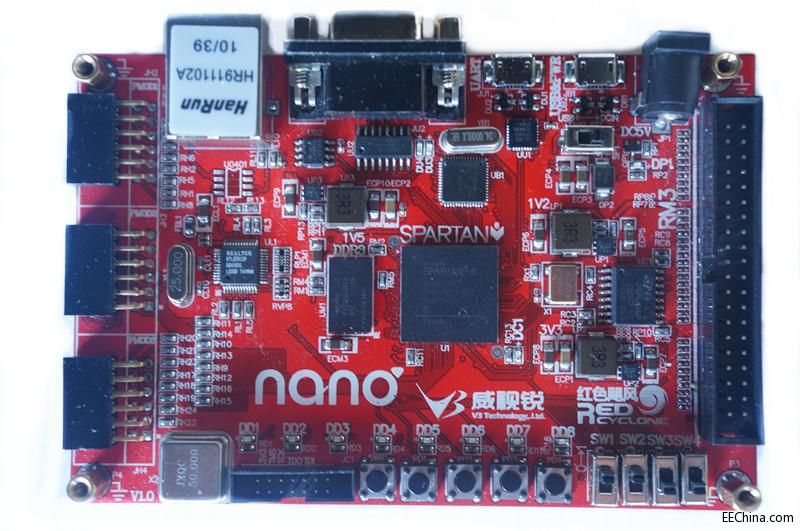

NANO2开发板实例之USB2.0接口通信回环

2014年03月24日 11:33 发布者:v3cyclone

NANO2开发板实例之 USB2.0接口通信回环基于FPGA实现USB2.0接口通信, USB2.0 PHY芯片是Cypress68013, 68013内部集成8051 内核,USB2.0芯片读写需要对8051核进行固件配置。一.FX2特性介绍1.1介绍Cypress Semiconductor公司的EZ-USB FX2是世界上第一款集成USB2.0的微处理器,它集成了USB2.0收发器、SIE(串行接口引擎)、增强的8051微控制器和可编程的外围接口。FX2这种独创性结构可使数据传输率达到56Mbytes/s,即USB2.0允许的最大带宽。在FX2中,智能SIE可以硬件处理许多USB1.1和USB2.0协议,从而减少了开发时间和确保了USB的兼容性。GPIF(General Programmable Interface)和主/从端点FIFO(8位或16位数据总线)为ATA、UTOPIA、EPP、PCMCIA和DSP等提供了简单和无缝连接接口。1.2结构CY7C68013结构图如图1所示。它有三种封装形式:56SSOP,100TQFP和128TQFP。

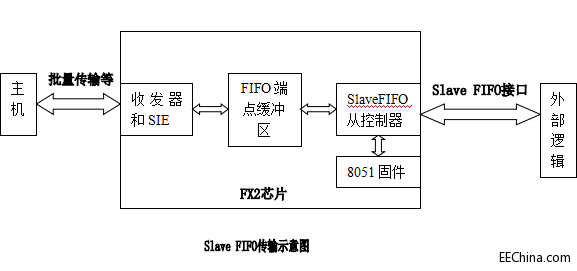

1.3特征★ 内嵌480MBit/s的收发器,锁相环PLL,串行接口引擎SIE——集成了整个USB 2.0协议的物理层。★ 为适应USB 2.0的480MBit/s的速率,FIFO端点可配置成2,3,4个缓冲区。★ 内嵌可工作在48MHz的增强型8051,它具有以下特征:- 具有256Byte的寄存器空间,两个串口,三个定时器,两个数据指针。- 四个机器周期(工作在48MHz下时为83.3ns)即组成一个指令周期。- 特殊功能寄存器(包括I/O口控制寄存器)可高速访问。- 应用USB向量中断,具有极短的ISR响应时间。- 只用作USB事务管理,控制,不参与数据传输,较好地解决了USB高速模式的带宽问题。★ “软配置”——USB固件可由USB总线下载,片上不需集成ROM。★ 拥有四个FIFO接口,可工作在内部或外部时钟下。端点和FIFO接口的应用使外部逻辑和USB总线可高速连接。★ 内嵌通用可编程接口GPIF,它是一个状态机,可充当主控制器,提供外部逻辑和USB总线的“无胶粘贴”。★ 一种单片USB 2.0外设解决方案,不需要外部的协议物理层,FX2把所有的功能集成在一个芯片上。二、Slave FIFO传输2.1概述当有一个与FX2芯片相连的外部逻辑只需要利用FX2做为一个USB 2.0接口而实现与主机的高速通讯,而它本身又能够提供满足Slave FIFO要求的传输时序,可以做为Slave FIFO主控制器时,即可考虑用此传输方式。Slave FIFO传输的示意图如下:

1.3特征★ 内嵌480MBit/s的收发器,锁相环PLL,串行接口引擎SIE——集成了整个USB 2.0协议的物理层。★ 为适应USB 2.0的480MBit/s的速率,FIFO端点可配置成2,3,4个缓冲区。★ 内嵌可工作在48MHz的增强型8051,它具有以下特征:- 具有256Byte的寄存器空间,两个串口,三个定时器,两个数据指针。- 四个机器周期(工作在48MHz下时为83.3ns)即组成一个指令周期。- 特殊功能寄存器(包括I/O口控制寄存器)可高速访问。- 应用USB向量中断,具有极短的ISR响应时间。- 只用作USB事务管理,控制,不参与数据传输,较好地解决了USB高速模式的带宽问题。★ “软配置”——USB固件可由USB总线下载,片上不需集成ROM。★ 拥有四个FIFO接口,可工作在内部或外部时钟下。端点和FIFO接口的应用使外部逻辑和USB总线可高速连接。★ 内嵌通用可编程接口GPIF,它是一个状态机,可充当主控制器,提供外部逻辑和USB总线的“无胶粘贴”。★ 一种单片USB 2.0外设解决方案,不需要外部的协议物理层,FX2把所有的功能集成在一个芯片上。二、Slave FIFO传输2.1概述当有一个与FX2芯片相连的外部逻辑只需要利用FX2做为一个USB 2.0接口而实现与主机的高速通讯,而它本身又能够提供满足Slave FIFO要求的传输时序,可以做为Slave FIFO主控制器时,即可考虑用此传输方式。Slave FIFO传输的示意图如下: 在这种方式下,FX2内嵌的8051固件的功能只是配置Slave FIFO相关的寄存器以及控制FX2何时工作在Slave FIFO模式下。一旦8051固件将相关的寄存器配置完毕,且使自身工作在Slave FIFO模式下后,外部逻辑(如FPGA)即可按照Slave FIFO的传输时序,高速与主机进行通讯,而在通讯过程中不需要8051固件的参与。2.2硬件连接(标准)在Slave FIFO方式下,外部逻辑与FX2的连接信号图如下:

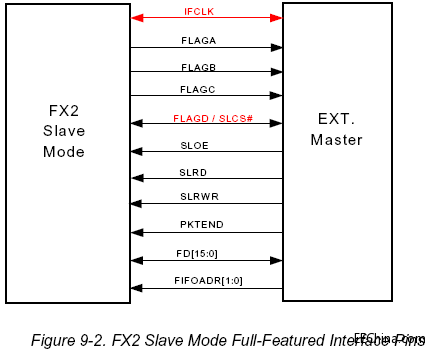

在这种方式下,FX2内嵌的8051固件的功能只是配置Slave FIFO相关的寄存器以及控制FX2何时工作在Slave FIFO模式下。一旦8051固件将相关的寄存器配置完毕,且使自身工作在Slave FIFO模式下后,外部逻辑(如FPGA)即可按照Slave FIFO的传输时序,高速与主机进行通讯,而在通讯过程中不需要8051固件的参与。2.2硬件连接(标准)在Slave FIFO方式下,外部逻辑与FX2的连接信号图如下: IFCLK:FX2输出的时钟,可做为通讯的同步时钟;FLAGA,FLAGB,FLAGC,FLAGD:FX2输出的FIFO状态信息,如满,空等;SLCS:FIFO的片选信号,外部逻辑控制,当SLCS输出高时,不可进行数据传输;SLOE:FIFO输出使能,外部逻辑控制,当SLOE无效时,数据线不输出有效数据;SLRD:FIFO读信号,外部逻辑控制,同步读时,FIFO指针在SLRD有效时的每个IFCLK的上升沿递增,异步读时,FIFO读指针在SLRD的每个有效—无效的跳变沿时递增;SLWR:FIFO写信号,外部逻辑控制,同步写时,在SLWR有效时的每个IFCLK的上升沿时数据被写入,FIFO指针递增,异步写时,在SLWR的每个有效—无效的跳变沿时数据被写入,FIFO写指针递增;PKTEND:包结束信号,外部逻辑控制,在正常情况下,外部逻辑向FX2的FIFO中写数,当写入FIFO端点的字节数等于FX2固件设定的包大小时,数据将自动被打成一包进行传输,但有时外部逻辑可能需要传输一个字节数小于FX2固件设定的包大小的包,这时,它只需在写入一定数目的字节后,声明此信号,此时FX2硬件不管外部逻辑写入了多少字节,都自动将之打成一包进行传输;FD:数据线;FIFOADR:选择四个FIFO端点的地址线,外部逻辑控制。2.3 Slave FIFO的几种传输方式2.3.1 同步Slave FIFO写同步Slave FIFO写的标准连接图如下:

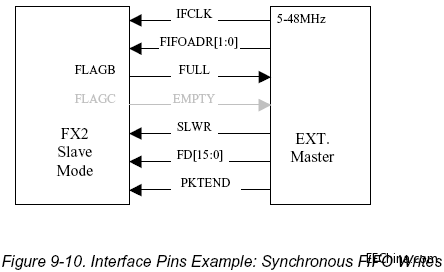

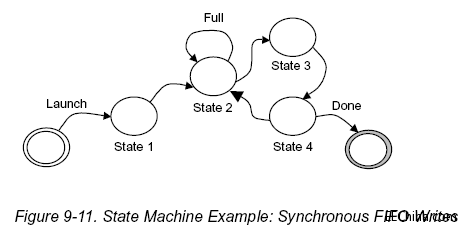

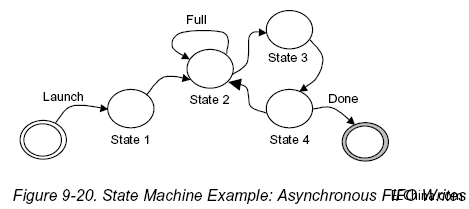

IFCLK:FX2输出的时钟,可做为通讯的同步时钟;FLAGA,FLAGB,FLAGC,FLAGD:FX2输出的FIFO状态信息,如满,空等;SLCS:FIFO的片选信号,外部逻辑控制,当SLCS输出高时,不可进行数据传输;SLOE:FIFO输出使能,外部逻辑控制,当SLOE无效时,数据线不输出有效数据;SLRD:FIFO读信号,外部逻辑控制,同步读时,FIFO指针在SLRD有效时的每个IFCLK的上升沿递增,异步读时,FIFO读指针在SLRD的每个有效—无效的跳变沿时递增;SLWR:FIFO写信号,外部逻辑控制,同步写时,在SLWR有效时的每个IFCLK的上升沿时数据被写入,FIFO指针递增,异步写时,在SLWR的每个有效—无效的跳变沿时数据被写入,FIFO写指针递增;PKTEND:包结束信号,外部逻辑控制,在正常情况下,外部逻辑向FX2的FIFO中写数,当写入FIFO端点的字节数等于FX2固件设定的包大小时,数据将自动被打成一包进行传输,但有时外部逻辑可能需要传输一个字节数小于FX2固件设定的包大小的包,这时,它只需在写入一定数目的字节后,声明此信号,此时FX2硬件不管外部逻辑写入了多少字节,都自动将之打成一包进行传输;FD:数据线;FIFOADR:选择四个FIFO端点的地址线,外部逻辑控制。2.3 Slave FIFO的几种传输方式2.3.1 同步Slave FIFO写同步Slave FIFO写的标准连接图如下: 同步Slave FIFO写的标准时序如下:IDLE:当写事件发生时,进状态1;状态1:使FIFOADR指向IN FIFO,进状态2;状态2:如FIFO满,在本状态等待,否则进状态3;状态3:驱动数据到数据线上,使SLWR有效,持续一个IFCLK周期,进状态4;状态4:如需传输更多的数,进状态2,否则进状态IDLE。状态跳转示意图如下:

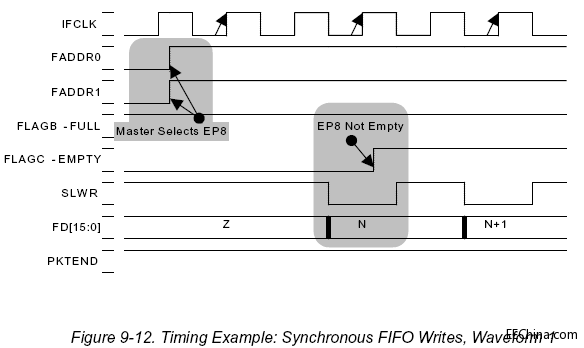

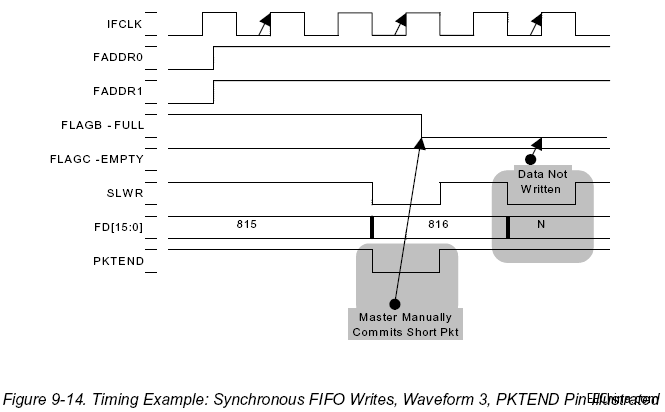

同步Slave FIFO写的标准时序如下:IDLE:当写事件发生时,进状态1;状态1:使FIFOADR指向IN FIFO,进状态2;状态2:如FIFO满,在本状态等待,否则进状态3;状态3:驱动数据到数据线上,使SLWR有效,持续一个IFCLK周期,进状态4;状态4:如需传输更多的数,进状态2,否则进状态IDLE。状态跳转示意图如下: 几种情况的时序图示意如下(FULL,EMPTY,SLWR,PKTEND均假定低有效):

几种情况的时序图示意如下(FULL,EMPTY,SLWR,PKTEND均假定低有效): 图示FIFO中本来没有数据,外部逻辑写入第一个数据时的情况。

图示FIFO中本来没有数据,外部逻辑写入第一个数据时的情况。 图示假定FX2设定包大小为512字节,外部逻辑向FIFO端点中写入的数据达512字节时的情况。此时FX2硬件自动将已写入的512字节打成一包准备进行传输,这个动作就和在普通传输中,FX2固件向FIFO端点中写入512字节后,把512这个数写入EPxBC中一样,只不过这个过程是由硬件自动完成的。在这里可以看出“FX2固件不参与数据传输过程”的含义了。外部逻辑只须按上面的时序图所示的时序向FIFO端点中一个一个字节(或字)地写数,写到一定数量,FX2硬件自动将数据打包传输,这一切均不需固件的参与,由此实现高速数据传输。

图示假定FX2设定包大小为512字节,外部逻辑向FIFO端点中写入的数据达512字节时的情况。此时FX2硬件自动将已写入的512字节打成一包准备进行传输,这个动作就和在普通传输中,FX2固件向FIFO端点中写入512字节后,把512这个数写入EPxBC中一样,只不过这个过程是由硬件自动完成的。在这里可以看出“FX2固件不参与数据传输过程”的含义了。外部逻辑只须按上面的时序图所示的时序向FIFO端点中一个一个字节(或字)地写数,写到一定数量,FX2硬件自动将数据打包传输,这一切均不需固件的参与,由此实现高速数据传输。 图示的是FIFO端点被写满时的情况。2.3.2 同步Slave FIFO读:同步Slave FIFO读的标准连接图如下:

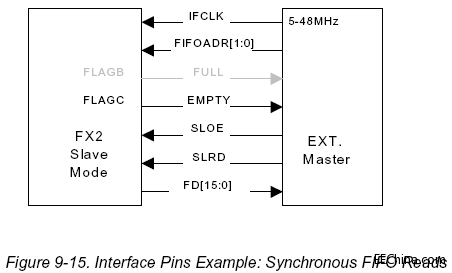

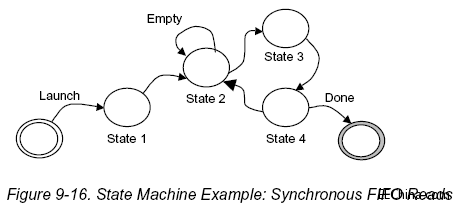

图示的是FIFO端点被写满时的情况。2.3.2 同步Slave FIFO读:同步Slave FIFO读的标准连接图如下: 同步Slave FIFO读的标准时序如下:IDLE:当读事件发生时,进状态1;状态1:使FIFOADR指向OUT FIFO,进状态2;状态2:使SLOE有效,如FIFO空,在本状态等待,否则进状态3;状态3:从数据线上读数,使SLRD有效,持续一个IFCLK周期,以递增FIFO读指针,进状态4;状态4:如需传输更多的数,进状态2,否则进状态IDLE。状态跳转示意图如下:

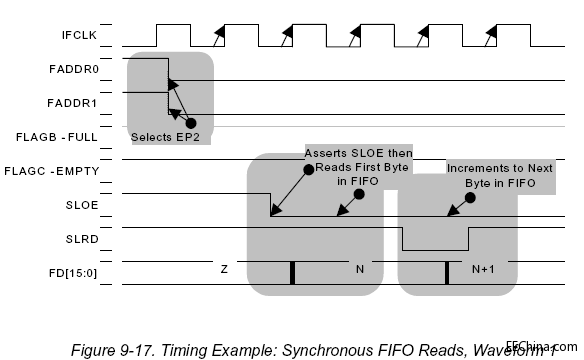

同步Slave FIFO读的标准时序如下:IDLE:当读事件发生时,进状态1;状态1:使FIFOADR指向OUT FIFO,进状态2;状态2:使SLOE有效,如FIFO空,在本状态等待,否则进状态3;状态3:从数据线上读数,使SLRD有效,持续一个IFCLK周期,以递增FIFO读指针,进状态4;状态4:如需传输更多的数,进状态2,否则进状态IDLE。状态跳转示意图如下: 几种情况的时序图示意如下(FULL,EMPTY,SLRD,SLOE均假定低有效):

几种情况的时序图示意如下(FULL,EMPTY,SLRD,SLOE均假定低有效): 图示正常情况时的时序。

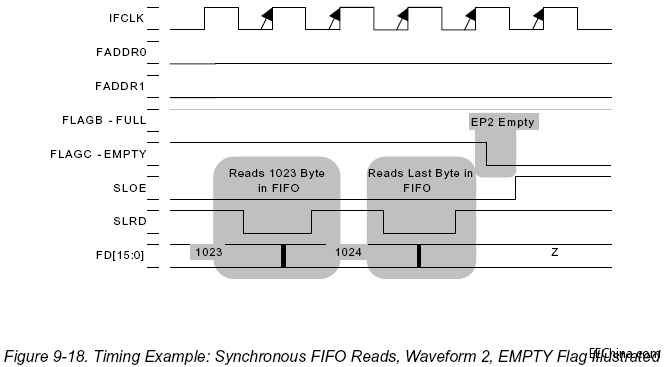

图示正常情况时的时序。 图示FIFO被读空时的情况。

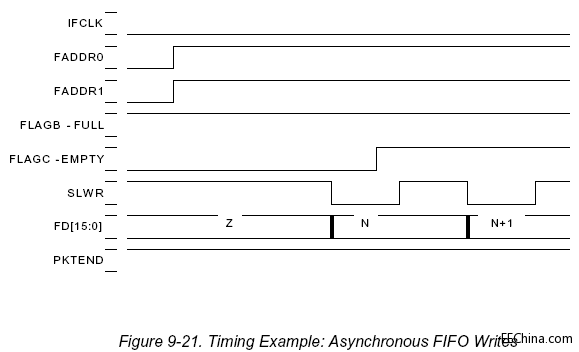

图示FIFO被读空时的情况。 几种情况的时序图示意如下(FULL,EMPTY,SLWR,PKTEND均假定低有效):

几种情况的时序图示意如下(FULL,EMPTY,SLWR,PKTEND均假定低有效): 图示FIFO中本来没有数据,外部逻辑写入第一个数据时的情况。三、测试USB接口:对于USB接口的测试,本次实验控制开发板上面的USB接口实现与PC机的通信。用usb2.0线连接pc与开发板usb接口,先下载s3_dram.bit程序,在没有掉电的情况下,打开相应的EZ-USB软件(ez-usb为usb2.0接口PC端驱动,安装文件在 “CY7C68013开发相关工具” 目录下)。在使用前,接上USB2.0接口到PC端,PC端设备管理器可以识别到USB设备,如果没有识别到USB设备,需要手动安装驱动,驱动文件为ezusbw2k.inf(测试目录下)的文件,手动选择inf所在目录。

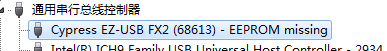

图示FIFO中本来没有数据,外部逻辑写入第一个数据时的情况。三、测试USB接口:对于USB接口的测试,本次实验控制开发板上面的USB接口实现与PC机的通信。用usb2.0线连接pc与开发板usb接口,先下载s3_dram.bit程序,在没有掉电的情况下,打开相应的EZ-USB软件(ez-usb为usb2.0接口PC端驱动,安装文件在 “CY7C68013开发相关工具” 目录下)。在使用前,接上USB2.0接口到PC端,PC端设备管理器可以识别到USB设备,如果没有识别到USB设备,需要手动安装驱动,驱动文件为ezusbw2k.inf(测试目录下)的文件,手动选择inf所在目录。 位置如图:

位置如图: 启动画面如下图:

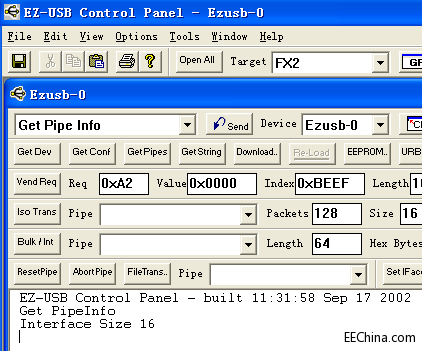

启动画面如下图: 上图表示连接可以进行下面测试,通过EZ_USB软件下载相应固件s3_dpram.bit程序,slavefifo.hex文件在“下载bit”目录下点击Download,

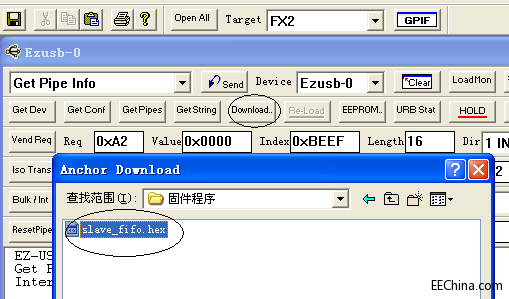

上图表示连接可以进行下面测试,通过EZ_USB软件下载相应固件s3_dpram.bit程序,slavefifo.hex文件在“下载bit”目录下点击Download, 双击打开相应读写的\usb接口VC程序(如下图)

双击打开相应读写的\usb接口VC程序(如下图) 看到写的测试现象,流过的数据速率。

看到写的测试现象,流过的数据速率。 应用平台 :红色飓风NANO2

应用平台 :红色飓风NANO2

http://www.fpgadev.com/shop_view.asp?id=96更多了解,请关注:NANO2用户资料链接 http://yunpan.cn/QpNRkwW9ZFnek

NANO2 论坛链接 http://www.zingsoc.com/forum/forum.php

NANO2 论坛链接 http://www.zingsoc.com/forum/forum.php  NANO2开箱视频演示http://v.youku.com/v_show/id_XNjgyMDM3NDQ0.html

NANO2开箱视频演示http://v.youku.com/v_show/id_XNjgyMDM3NDQ0.html 关于这款开发板,请关注新浪微博及博客 http://weibo.com/u/5061825906 http://blog.sina.com.cn/u/5061825906

关于这款开发板,请关注新浪微博及博客 http://weibo.com/u/5061825906 http://blog.sina.com.cn/u/5061825906